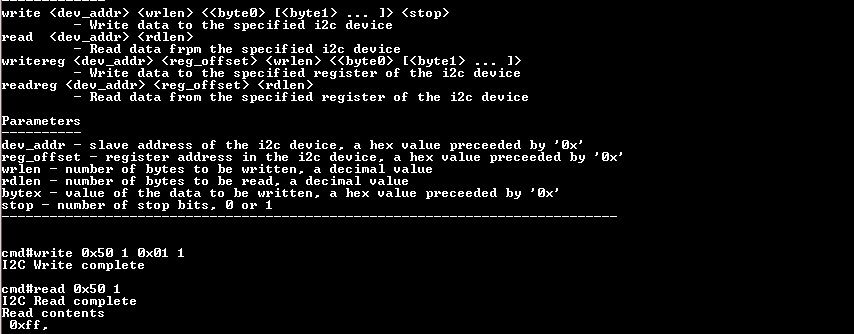

Tool/software: Code Composer Studio

I am interfacing CC3200 with below EEPROM (AT24C) . It is obvious that I2C demo should work fine for any I2C device by just putting correct device id (Here for me Device id is 0x50) in example code.

Below are my observation/ problems

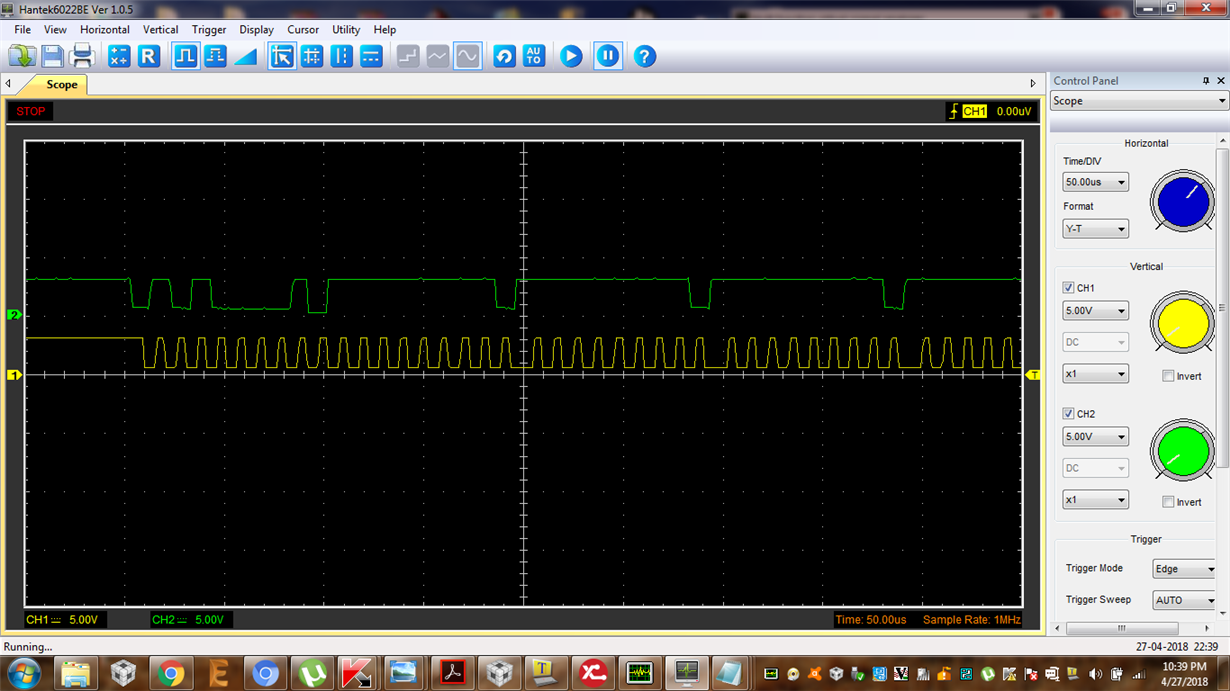

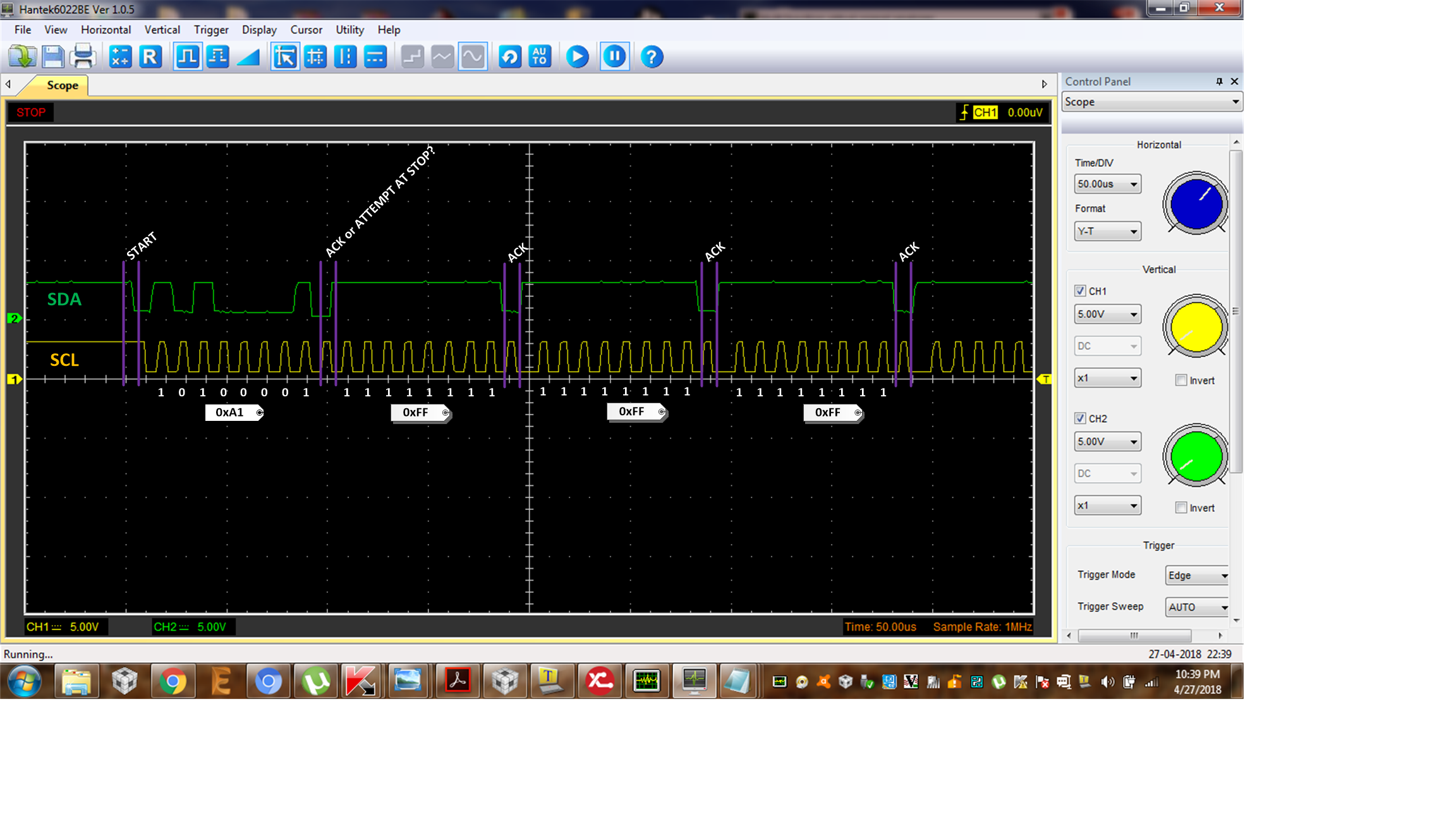

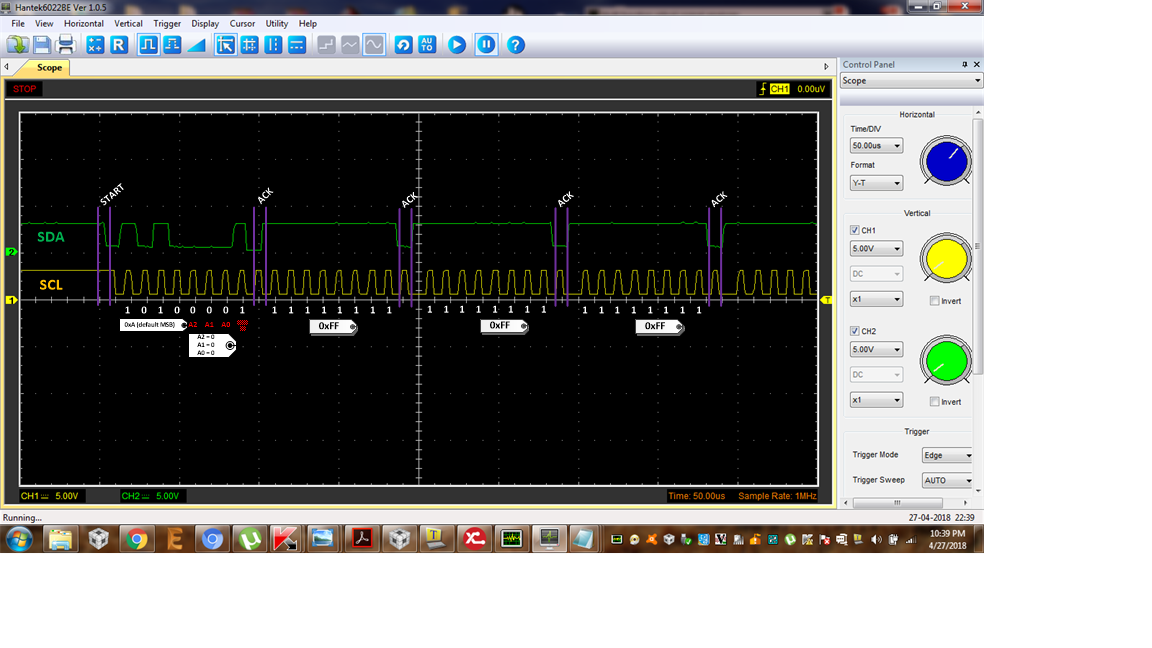

1, If i am writing in EEPROM by either write cmd or write reg cmd in tera term result is I2C write complete.

2. Now after writing if i am reading by either read or read reg command in tera team always i get 0XFF.

3. If i read full 255 location of EEPROM result are 0Xff always.

4. It seems that i am not able to write anything in EEPROM. So i tried to 7 bit addressing by replacing device id 0x50 to 0x51 for write operation but its result says ERROR IN PROCESSING CMD. WP pin of EEPROM is grounded .

5. I am using 3.3volt pullup for SDA and SCL line . I got from data sheet for FST mode 400kbps speed VCC should be 5 volt hence i have replaced fast mode to std mode in the code.

I struggled alot can anybody tell me what is the problem in writing I2C EEPROM ??

screen shot are