Other Parts Discussed in Thread: WL1801, WL1271, WL1837, , WL1837MOD

WL1801 has replaced TiWI-BLE (WL1271) in a design using i.MX6 (ARM) platform.

OS is yocto 3.10

Wilink8 is used. Ti-compat-wireless 3.11.18-r8.a9.22

TiWI-BLE used SMD_CLK of 25MHz while WL1801 run at 50MHz.

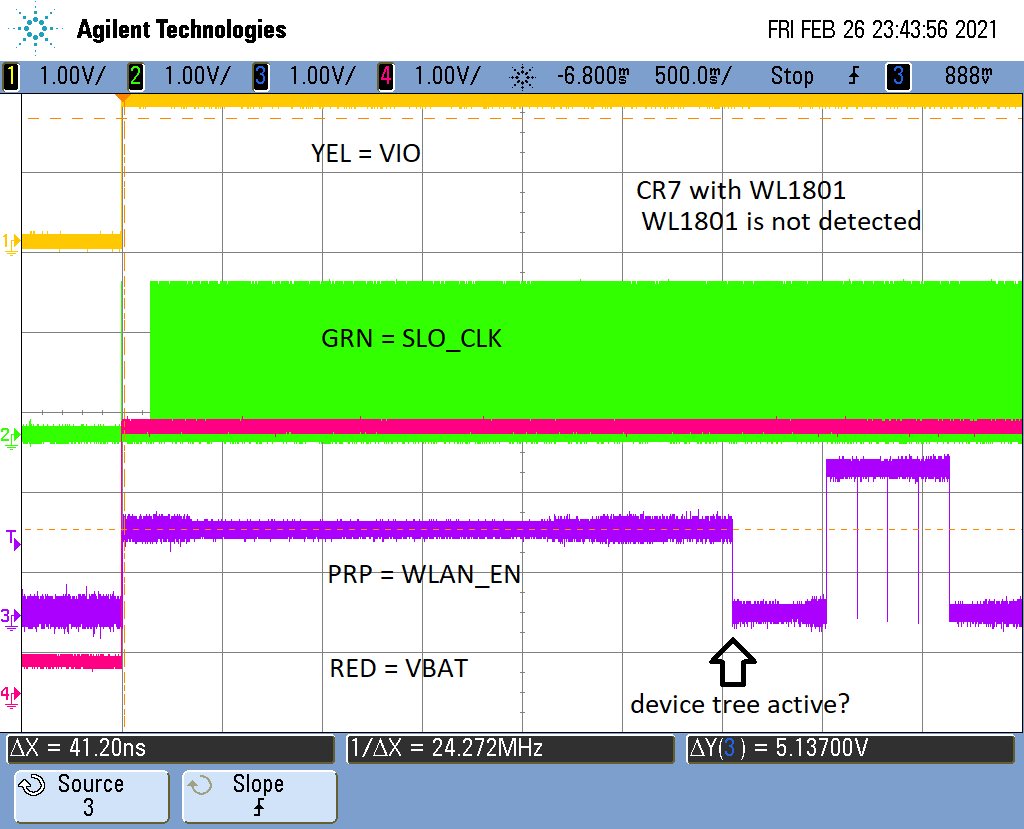

I have 0.3% failure rate with WL1801. The WL1801 fails to be detected.

Can I limit the SMD_CLK to 25MHz with WL1801? I want to see if the slower clock rate would impact the failure rate.

Setting max-frequency = <25000000>; in the device tree did not influence it.