Hello community,

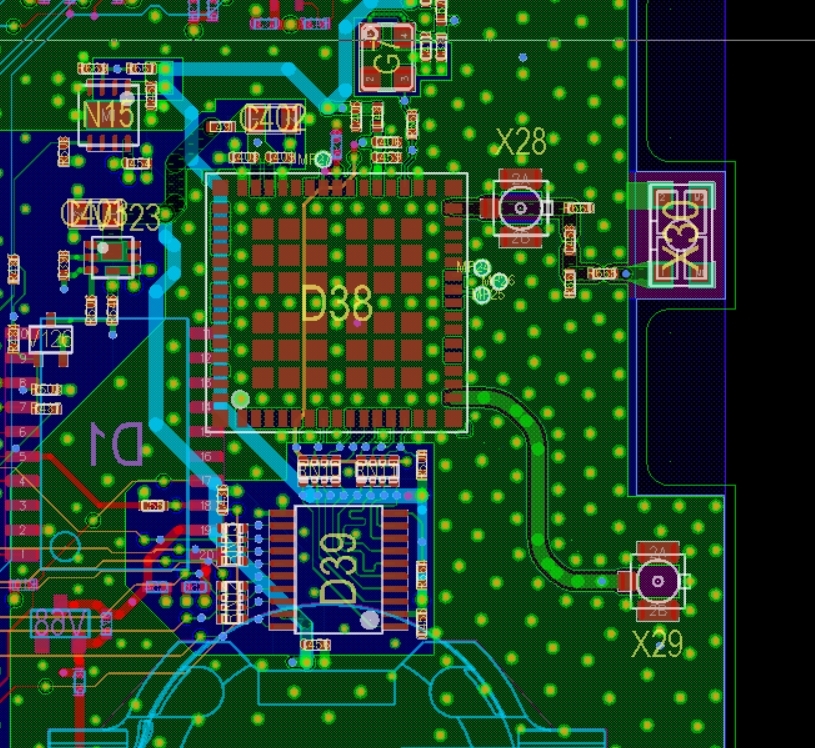

I have some trouble with our WL1807 design (see schematic attached).

When we are testing our design with higher temperature like 60 °C we get an error at initializing.

The error do not occurs at lower temperature, we also tested it in climate cabinet with 0 °C and 40 °C. The error occurs only at 40 °C above.

Our logfiles looks like:

[2019-04-19 23:41:23.928] [ 1.937343] mmc1: queuing unknown CIS tuple 0x91 (3 bytes)

[2019-04-19 23:41:23.928] [ 1.938922] mmc1: new high speed SDIO card at address 0001

[2019-04-19 23:41:28.502] [ 6.657544] fw_get_filesystem_firmware: path = /lib/firmware/updates/4.1.15-rel_imx_4.1.15_2.0.0_ga-20170202-IF40-/ti-connectivity/wl1271-nvs.bin

[2019-04-19 23:41:28.555] [ 6.693241] fw_get_filesystem_firmware: file = 0xfffffffe, IS_ERR = 1

[2019-04-19 23:41:28.555] [ 6.699699] trying next...

[2019-04-19 23:41:28.751] [ 6.715314] fw_get_filesystem_firmware: path = /lib/firmware/updates/ti-connectivity/wl1271-nvs.bin

[2019-04-19 23:41:28.751] [ 6.732582] fw_get_filesystem_firmware: file = 0xfffffffe, IS_ERR = 1

[2019-04-19 23:41:28.751] [ 6.743539] trying next...

[2019-04-19 23:41:28.751] [ 6.752620] fw_get_filesystem_firmware: path = /lib/firmware/4.1.15-rel_imx_4.1.15_2.0.0_ga-20170202-IF40-/ti-connectivity/wl1271-nvs.bin

[2019-04-19 23:41:28.751] [ 6.766529] fw_get_filesystem_firmware: file = 0xfffffffe, IS_ERR = 1

[2019-04-19 23:41:28.751] [ 6.774324] trying next...

[2019-04-19 23:41:28.751] [ 6.777504] fw_get_filesystem_firmware: path = /lib/firmware/ti-connectivity/wl1271-nvs.bin

[2019-04-19 23:41:28.751] [ 6.787386] fw_get_filesystem_firmware: file = 0xa896d3c0, IS_ERR = 0

[2019-04-19 23:41:28.751] [ 6.795109] fw_get_filesystem_firmware: path = /lib/firmware/updates/4.1.15-rel_imx_4.1.15_2.0.0_ga-20170202-IF40-/ti-connectivity/wl18xx-conf.bin

[2019-04-19 23:41:28.751] [ 6.809269] fw_get_filesystem_firmware: file = 0xfffffffe, IS_ERR = 1

[2019-04-19 23:41:28.751] [ 6.815995] trying next...

[2019-04-19 23:41:28.751] [ 6.818878] fw_get_filesystem_firmware: path = /lib/firmware/updates/ti-connectivity/wl18xx-conf.bin

[2019-04-19 23:41:28.751] [ 6.828389] fw_get_filesystem_firmware: file = 0xfffffffe, IS_ERR = 1

[2019-04-19 23:41:28.753] [ 6.835086] trying next...

[2019-04-19 23:41:28.753] [ 6.838258] fw_get_filesystem_firmware: path = /lib/firmware/4.1.15-rel_imx_4.1.15_2.0.0_ga-20170202-IF40-/ti-connectivity/wl18xx-conf.bin

[2019-04-19 23:41:28.753] [ 6.852046] fw_get_filesystem_firmware: file = 0xfffffffe, IS_ERR = 1

[2019-04-19 23:41:28.753] [ 6.859054] trying next...

[2019-04-19 23:41:28.753] [ 6.862174] fw_get_filesystem_firmware: path = /lib/firmware/ti-connectivity/wl18xx-conf.bin

[2019-04-19 23:41:28.754] [ 6.871360] fw_get_filesystem_firmware: file = 0xa896db40, IS_ERR = 0

[2019-04-19 23:41:28.754] [ 6.887367] FAT-fs (mmcblk0p1): Volume was not properly unmounted. Some data may be corrupt. Please run fsck.

[2019-04-19 23:41:28.766] [ 6.919626] wlcore: ERROR couldn't get hw info

The SDIO-Interface recognize the WL1807 but it seems that the error will occuring while loading the firmware.

I also tested to add 10k pullups at CMD, CLK and DATA0-3 on 1.8V logic, 3.3V logic and as well on both sides at the same time.

But the error still occurs.

I need some help.

Thank you in advance.

Best regards,

Juergen