Hi TI support teams,

I am now re-designing a previous Iot product for a certain customer .

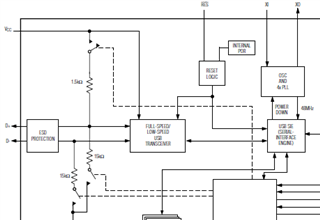

That product is using the CC2531 radio CPU and using embedded USB port.

I am now concerning about power on/off function change regarding USB and CPU power sequence.

Under previous specification, power on is caused by USB insert and VBUS arise,

and power off is caused by USB connector disconnection.

This is simple and same as dongle, but the product has LiPO battery backup also , so the customer is requiring that the power on/off should be controled by a soft switch not by USB connection.

But we are concerning about problem would be happen that the USB DP/DM signal is provided on the CPU port during CPU powered down under this new specification.

I'm wondering these are USB PHY input port, therefore such situation would be allowed, right?

Attached pictures are USB input and CC2531 DP/DM schematic.

Could you please kindly help us ?

Your support would be highly appreciated.

Best regards,

Yoshiaki Maehara