We found a GPIO setting to edge interrupt mode, when GPIO input voltage change from 3.3V to 0.58V, a interrupt will be trigged. If this is a issue? Or edge detection mechanism is not related about GPIO level detection?

Below capture from TI DOC:

7.4 General-Purpose I/O Interrupts

General-purpose I/O pins configured as inputs can be used to generate interrupts. The interrupts can be

configured to trigger on either a rising or falling edge of the external signal.

indicates a one-shot, either due to the level source or due to edge

shaping. Interrupts missing this are to be treated as level-triggered (apply to ports P0, P1, and P2). The

switch boxes are shown in the default state, and or indicates rising- or falling-edge detection, that

is, at what time instance the interrupt is generated.

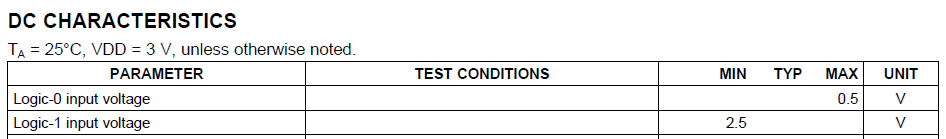

That can be found in USER GUIDE(SWRU191). Also can found a description in DATASHEET(SWRS086) as IO input parameter:

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Logic-0 input voltage 0.5 V