Greetings,

I am working on a custom dm8148 board and we have a hdmi rx to feed stereo I2S audio data to the McAsp of Davinci.

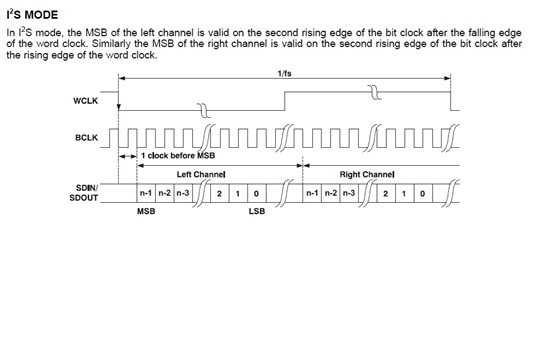

When I trying to modify audio format in davinic-evm.c from SND_SOC_DAIFMT_DSP_B to SND_SOC_DAIFMT_I2S, I can only get either left or right channel data.

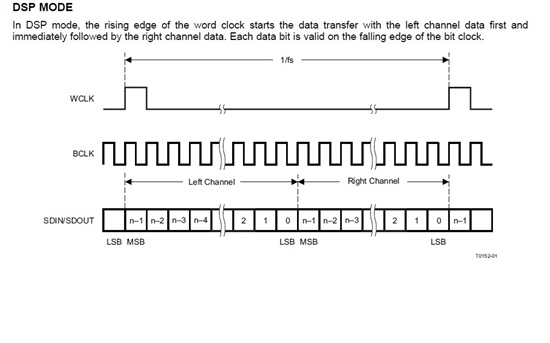

Then I checked the davinci-mcasp.c driver file and found that it seems right now McAsp only support DSP mode.

It is okay for tlv320 analog decoder, cuz it support either I2S or DSP mode, however it is a big issue for us. We only have standard I2S audio data from our HDMI rx.

Could any TI employee clarify this for us, in the datasheet of DAvinci 8148, it clearly claim support I2S mode however, in the driver only support DSP_B mode?

How can I set the registers to support standard I2S mode? I hope this is only a driver side limitation.

Regards,

Jun Zhang

=====================================

static void davinci_hw_param(struct davinci_audio_dev *dev, int stream)

{

int i, active_slots;

u32 mask = 0;

active_slots = (dev->tdm_slots > 31) ? 32 : dev->tdm_slots;

for (i = 0; i < active_slots; i++)

mask |= (1 << i);

mcasp_clr_bits(dev->base + DAVINCI_MCASP_ACLKXCTL_REG, TX_ASYNC);

if (stream == SNDRV_PCM_STREAM_PLAYBACK) {

/* bit stream is MSB first with no delay */

/* DSP_B mode */

mcasp_set_bits(dev->base + DAVINCI_MCASP_AHCLKXCTL_REG,

AHCLKXE);

mcasp_set_reg(dev->base + DAVINCI_MCASP_TXTDM_REG, mask);

mcasp_set_bits(dev->base + DAVINCI_MCASP_TXFMT_REG, TXORD);

if ((dev->tdm_slots >= 2) || (dev->tdm_slots <= 32))

mcasp_mod_bits(dev->base + DAVINCI_MCASP_TXFMCTL_REG,

FSXMOD(dev->tdm_slots), FSXMOD(0x1FF));

else

printk(KERN_ERR "playback tdm slot %d not supported\n",

dev->tdm_slots);

mcasp_clr_bits(dev->base + DAVINCI_MCASP_TXFMCTL_REG, FSXDUR);

} else {

/* bit stream is MSB first with no delay */

/* DSP_B mode */

mcasp_set_bits(dev->base + DAVINCI_MCASP_RXFMT_REG, RXORD);

mcasp_set_bits(dev->base + DAVINCI_MCASP_AHCLKRCTL_REG,

AHCLKRE);

mcasp_set_reg(dev->base + DAVINCI_MCASP_RXTDM_REG, mask);

if ((dev->tdm_slots >= 2) || (dev->tdm_slots <= 32))

mcasp_mod_bits(dev->base + DAVINCI_MCASP_RXFMCTL_REG,

FSRMOD(dev->tdm_slots), FSRMOD(0x1FF));

else

printk(KERN_ERR "capture tdm slot %d not supported\n",

dev->tdm_slots);

mcasp_clr_bits(dev->base + DAVINCI_MCASP_RXFMCTL_REG, FSRDUR);

}

}