Hi,

I would like to ask a question on I2C controller (DM6437)'s communication with OV SCCB.

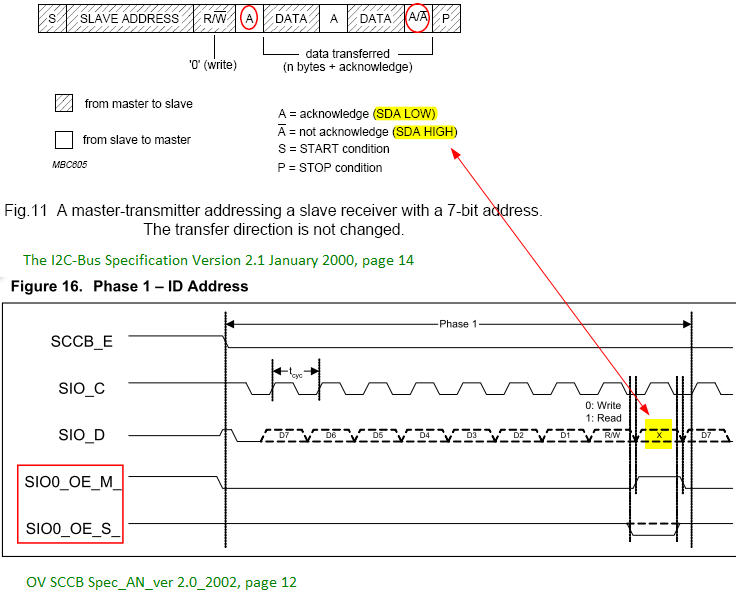

A difference between I2C is that for I2C there is an ACK (acknowledgement) bit (9th bit) after each byte of transmission, but for SCCB this 9th bit is "Don't care".

For standard I2C in master transmit mode, the slave is supposed to acknowledge the byte sent by the master by pulling down the SDA during the ACK bit time; however for OV SCCB, it seems that “Don’t care” bit can take either 0 or 1 and is not functionally doing any “acknowledgement”.

The problem is on the master side. In I2C, the master (according to my understanding) is going to read SDA during the ACK time: If ACK is low, then it would then know the previous byte has been successfully sent and then it will proceed to the next byte or stop; if ACK is high, something else will happen (I am not quite clear on what will happen here). Anyway, we see that in standard I2C the master is expecting a meaningful ACK bit from the slave after sending each byte.

However for SCCB, since the 9th bit is “Don’t care”, the slave can either keep SDA high or pull it low during this I2C’s ACK time. So if it chose to keep SDA high, what will happen when master reads SDA to know the acknowledgement status of the slave? Won’t it interpret the high SDA as a signal that the slave hasn’t successfully received the data? Would the master still proceed regardless of the high SDA bit, abort the process, or repeat the previous transaction (sending)?

This is my question on why DaVinci’s I2C controller can communicate with SCCB. Could anyone help on this?

Zheng