Hello,

I tried to establish an SPI communication between EVM TMS320DM6437 (slave) and a module CHEETAH (master).

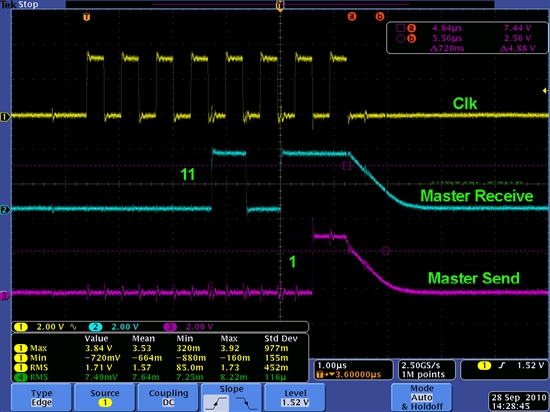

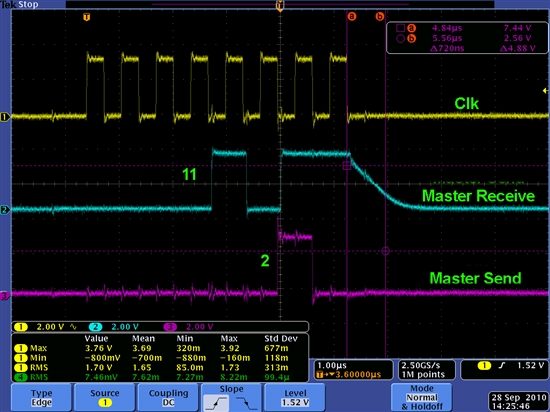

For the packets transmitted from the CHEETAH there are no problem. But I have a small problem with the two first packets sent from the DSP because the first packet is repeated twice then the transmission become correct.

I don't know what could be the problem?

Also, I found a problem in the configuration of Clock stop mode since I configured the EVM in Clock stop mode 0 (CLKSTP = 10b et CLKXP = 0).

On the other hand, to have the correct transmission of packets the CHEETAH must be configured in Clock stop mode 1, I cheked the other modes but the value of packets exchanged was wrong.

Is there an explication for this?

Any suggestion would be appreciated.