Hi all,

I am working on our custom design that contains a C6748 (@456MHz) and a Cyclone IV FPGA that is connected to the EMIFA. Via CS3 I can access several registers on the FPGA, via CS4 we can do USB-communication. I wrote a none-bios-application that polls our USB-communication in the main-loop, works nice.

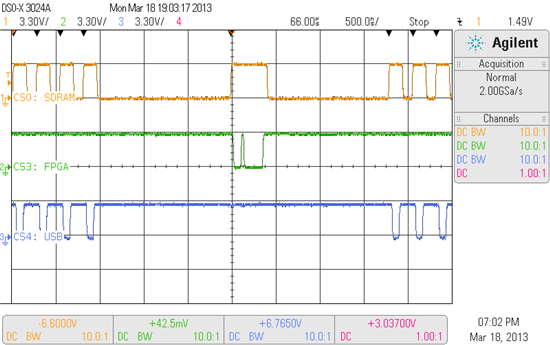

I have set up a timer that generates Interrupts with 10kHz. When the interrupt occurs, the DSP reads and writes some registers on the FPGA, that works too. But when I watched the different chip-selects by oscilloscope to determine the workload of the EMIFA, I saw a big latency in the execution of the timer-interrupt. I attached a screenshot of the oscilloscope.

You can see the polling of the USB-connection in blue, then the interrupt occurs, but there is about 1500ns stall where nothing happens on the EMIFA. Then there are the read/write-operations on the FPGA and another stall afterwards. I tried nearly everything I could imagine, but it doesn't change much (Debug<->Release, optimizations, inlining...).

The main-loop solely consists (after the initialisation) of a while(1) that polls the USB-connection via a HWREG(). In the interrupt I followed the starterware-examples to reset the flags (TimerIntDisable, IntEventClear, TimerIntStatusClear) and only do 2 operations on the EMIFA , also via HWREG(). By the way, the program is in L2RAM located.

Does anyone know the origin of that latency and/or how to remove it?

Thanks,

Chris