CCSv5, using C5515 DSP.

Can someone explain the meaning of TIMINT in the register view of the C5515 debug?

TIMER1

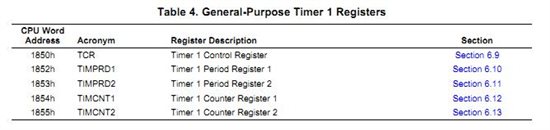

TCR 0x8000 Memory Mapped Register: Timer Control

TIMPRD1 0x3A34 Memory Mapped Register: Timer period LSW

TIMPRD2 0x0000 Memory Mapped Register: Timer period MSW

TIMCNT1 0x0000 Memory Mapped Register: Timer Counter LSW

TIMCNT2 0x0000 Memory Mapped Register: Timer Counter MSW

TIMINT 0x0001 Memory Mapped Register: Timer interrupt

I cannot find this in the Timer User Guide (sprufo2). Here are the registers listed in the guide.

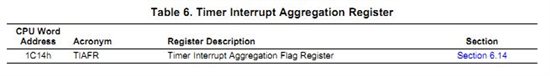

The other pertinent register is the timer interrupt aggregation register, which is located at 0x1c14h.

However, when I reset the Timer 1 interrupt bit in the TIAFR, the TIMINT bit does not get reset.

What is the TIMINT bit and why does it appear in the register view of the C5515 debug screen?