Dear,

Could someone give me your advise for my 2 questions?

Related posts:

http://e2e.ti.com/support/dsp/tms320c5000_power-efficient_dsps/f/109/t/188754.aspx

Device: TMS320VC5507ZHH

I can not get measured value that should be equal with calculated value of AD Conversion time.

Therefore, I would like to confirm my understandings.

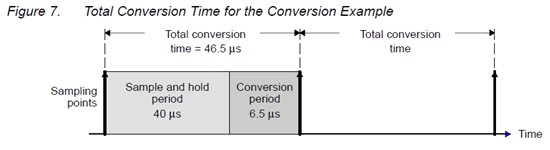

TMS320VC5507/5509 DSP ADC Reference Guide(spru586b), have "6 Conversion Example" in page 16 and 17.

In "6 Conversion Example", Total Conversion Time is set as 46.5us with following parameters.

CPUCLKDIV = 00100011

CONVRATEDIV = 0000

SAMPTIMEDIV = 01001111

System Clock = 144MHz

I hope I could get "Total Conversion Time = 46.5us", calculated value with above parameters those are same as "6 Conversion Example" in page 16 and 17 with my board.

But I can not get the 46.5us with my board, TMS320VC5509A EVM PLUS.

I could get these Total Conversion Times with "feature of measure cycle in CCS":

14.9us

16.3us

16.2us

I measured during ADCBUSY=1.

I'm not sure whether my measurement way for "Total conversion time" is correct or not.

My question:

Question 1.

I think Total Conversion Time for the Conversion is predictive and deterministic.

In other words, in case of the "6 Conversion Example", the Total Conversion Time should NOT be shorten from 46.5us.

Am I right?

Question 2.

I think there is nothing but following 2 constraint for setting Total Conversion TIme.

ADC Conversion Clock ≦ 2MHz

40uS ≦ ADC Sample and Hold Period

Am I right?

Regards,

Okayama