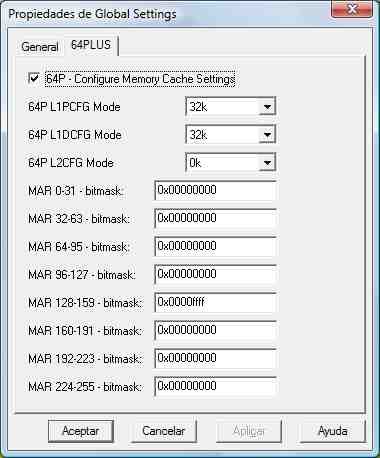

I can see at line 84 in audioSample_io.c a BUFALING definition for L2 cache so I assume that L2 cache will be used. However, Global Settings in audioSample.tcf shows the next dialog

Cache settings is enabled but no memory size is assinged to L2CFG Mode, why? Moreover MAR 128-159 bits are setting to 0x0000ffff that signifies that 256MB of memory is cacheable beginning at address 0x80000000. My board is an OMAP-L137 EVM so I believe this has not sense. I think MAR bits should be setting from 192-223 with a bitmask of 0x0000000F that match with my EVM board. Could anyone confirm this? I do not understand provided audio example configuration. Thanks in advance, gaston