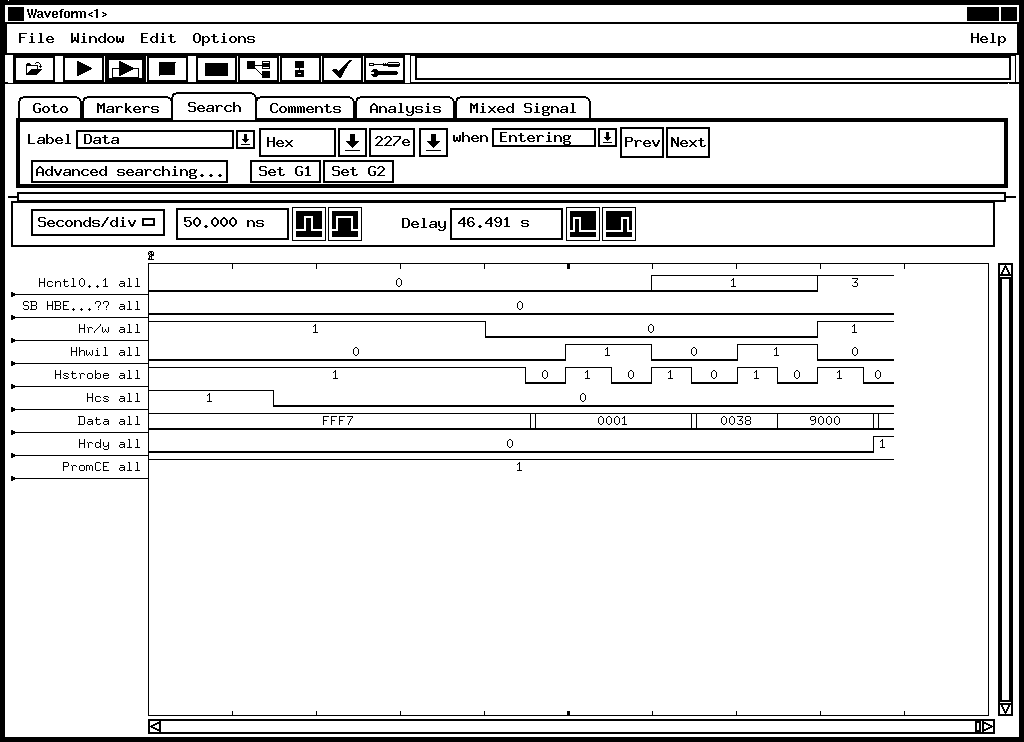

I have a 6713 design where some HPI reads from the CE1 address space (0x9000 0000) cause the HRDY signal to stay high.

All the writes to the HPI from the host (a FPGA is the host side of the HPI) seem to work fine. After writing, I try to read (often from the same address as a write) and some times the read works fine, and sometimes HRDY stays high indefinitely. If I do multiple reads from the same address, I may get one or two good reads in a row then it will fail.

I've looked at signal integrity (on the HDS1 signal) and timing and don't see any questionable issues. The implementation is HDS2 and HAS are tied high and HDS1 is used for the strobe. The protocol, as I read the 6XXX HPI reference guide, is correct, and the same for the good and bad cases.

The only way to clear the HRDY signal after this happens is to reset the DSP. If I restart the DSP and repeat the sequence of writes followed by reads, the behavior is the same.

Any ideas on where to go from here?