Tool/software: Code Composer Studio

Hi

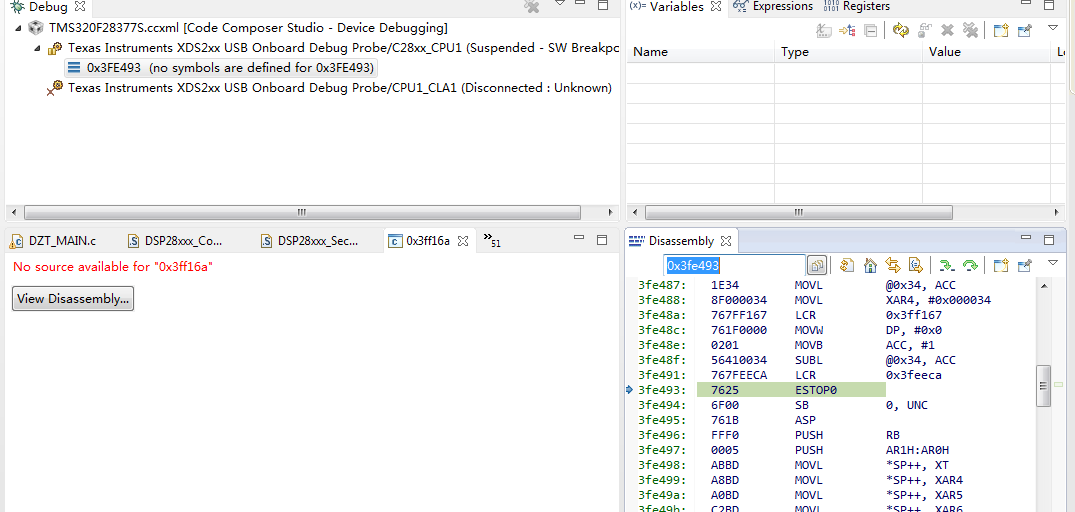

I have a trouble recently when I develop a project using 28377. I try to run my app in the sram load from flash, acourding to "SPRAAU8A" apprach, add the file "DSP28xxx_SectionCopy_nonBIOS.asm" and change the file "F2837xS_CodeStartBranch.asm" instead of the "DSP28xxx_CodeStartBranch.asm". but afer build project and load, the CCS halt at 0x3fe493 before jump to main(). so can anyone help me?

by the way, my app is run correctly when load to ram and load to flash that not use bootloader.

"DSP28xxx_CodeStartBranch.asm" content below:

WD_DISABLE .set 1 ;set to 1 to disable WD, else set to 0

.ref copy_sections

.global code_start

***********************************************************************

* Function: codestart section

*

* Description: Branch to code starting point

***********************************************************************

.sect "codestart"

code_start:

.if WD_DISABLE == 1

LB wd_disable ;Branch to watchdog disable code

.else

LB copy_sections ;Branch to copy_sections

.endif

;end codestart section

***********************************************************************

* Function: wd_disable

*

* Description: Disables the watchdog timer

***********************************************************************

.if WD_DISABLE == 1

.text

wd_disable:

SETC OBJMODE ; Set OBJMODE for 28x object code

EALLOW ; Enable EALLOW protected register access

MOVZ DP, #7029h>>6 ; Set data page for WDCR register

MOV @7029h, #0068h ; Set WDDIS bit in WDCR to disable WD

EDIS ;Disable EALLOW protected register access

LB copy_sections ;Branch to copy_sections

.endif

"DSP28xxx_SectionCopy_nonBIOS.asm" content below:

.ref _c_int00

.global copy_sections

.global _cinit_loadstart, _cinit_runstart, _cinit_size

.global _const_loadstart, _const_runstart, _const_size

.global _econst_loadstart, _econst_runstart, _econst_size

.global _pinit_loadstart, _pinit_runstart, _pinit_size

.global _switch_loadstart, _switch_runstart, _switch_size

.global _text_loadstart, _text_runstart, _text_size

***********************************************************************

* Function: copy_sections

*

* Description: Copies initialized sections from flash to ram

***********************************************************************

.sect "copysections"

copy_sections:

MOVL XAR5,#_cinit_size ; Store Section Size in XAR5

MOVL ACC,@XAR5 ; Move Section Size to ACC

MOVL XAR6,#_cinit_loadstart ; Store Load Starting Address in XAR6

MOVL XAR7,#_cinit_runstart ; Store Run Address in XAR7

LCR copy ; Branch to Copy

MOVL XAR5,#_const_size ; Store Section Size in XAR5

MOVL ACC,@XAR5 ; Move Section Size to ACC

MOVL XAR6,#_const_loadstart ; Store Load Starting Address in XAR6

MOVL XAR7,#_const_runstart ; Store Run Address in XAR7

LCR copy ; Branch to Copy

MOVL XAR5,#_econst_size ; Store Section Size in XAR5

MOVL ACC,@XAR5 ; Move Section Size to ACC

MOVL XAR6,#_econst_loadstart ; Store Load Starting Address in XAR6

MOVL XAR7,#_econst_runstart ; Store Run Address in XAR7

LCR copy ; Branch to Copy

MOVL XAR5,#_pinit_size ; Store Section Size in XAR5

MOVL ACC,@XAR5 ; Move Section Size to ACC

MOVL XAR6,#_pinit_loadstart ; Store Load Starting Address in XAR6

MOVL XAR7,#_pinit_runstart ; Store Run Address in XAR7

LCR copy ; Branch to Copy

MOVL XAR5,#_switch_size ; Store Section Size in XAR5

MOVL ACC,@XAR5 ; Move Section Size to ACC

MOVL XAR6,#_switch_loadstart ; Store Load Starting Address in XAR6

MOVL XAR7,#_switch_runstart ; Store Run Address in XAR7

LCR copy ; Branch to Copy

MOVL XAR5,#_text_size ; Store Section Size in XAR5

MOVL ACC,@XAR5 ; Move Section Size to ACC

MOVL XAR6,#_text_loadstart ; Store Load Starting Address in XAR6

MOVL XAR7,#_text_runstart ; Store Run Address in XAR7

LCR copy ; Branch to Copy

LB _c_int00 ; Branch to start of boot.asm in RTS library

copy:

B return,EQ ; Return if ACC is Zero (No section to copy)

SUBB ACC,#1

RPT AL ; Copy Section From Load Address to

|| PWRITE *XAR7, *XAR6++ ; Run Address

return:

LRETR ; Return

.end

CMD content below:

MEMORY

{

PAGE 0 : /* Program Memory */

/* Memory (RAM/FLASH) blocks can be moved to PAGE1 for data allocation */

/* BEGIN is used for the "boot to Flash" bootloader mode */

BEGIN : origin = 0x080000, length = 0x000002

RAMM0 : origin = 0x000122, length = 0x0002DE

RAMD0 : origin = 0x00B000, length = 0x000800

RAMLS : origin = 0x008000, length = 0x003000

RESET : origin = 0x3FFFC0, length = 0x000002

/* Flash sectors */

FLASHA : origin = 0x080002, length = 0x001FFE /* on-chip Flash */

FLASHB : origin = 0x082000, length = 0x07E000 /* on-chip Flash */

PAGE 1 : /* Data Memory */

/* Memory (RAM/FLASH) blocks can be moved to PAGE0 for program allocation */

BOOT_RSVD : origin = 0x000002, length = 0x000120 /* Part of M0, BOOT rom will use this for stack */

RAMM1 : origin = 0x000400, length = 0x000400 /* on-chip RAM block M1 */

RAMD1 : origin = 0x00B800, length = 0x000800

RAMGS : origin = 0x00C000, length = 0x010000

}

SECTIONS

{

/* Allocate program areas: */

codestart : > BEGIN PAGE = 0, ALIGN(4)

copysections : > FLASHB PAGE = 0, ALIGN(4)

/*** Initialized Sections ***/

.cinit : LOAD = FLASHB, PAGE = 0 /* can be ROM */

RUN = RAMLS, PAGE = 0 /* must be CSM secured RAM */

LOAD_START(_cinit_loadstart),

RUN_START(_cinit_runstart),

SIZE(_cinit_size)

.const : LOAD = FLASHB, PAGE = 0 /* can be ROM */

RUN = RAMLS, PAGE = 0 /* must be CSM secured RAM */

LOAD_START(_const_loadstart),

RUN_START(_const_runstart),

SIZE(_const_size)

.econst : LOAD = FLASHB, PAGE = 0 /* can be ROM */

RUN = RAMLS, PAGE = 0 /* must be CSM secured RAM */

LOAD_START(_econst_loadstart),

RUN_START(_econst_runstart),

SIZE(_econst_size)

.pinit : LOAD = FLASHB, PAGE = 0 /* can be ROM */

RUN = RAMLS, PAGE = 0 /* must be CSM secured RAM */

LOAD_START(_pinit_loadstart),

RUN_START(_pinit_runstart),

SIZE(_pinit_size)

.switch : LOAD = FLASHB, PAGE = 0 /* can be ROM */

RUN = RAMLS, PAGE = 0 /* must be CSM secured RAM */

LOAD_START(_switch_loadstart),

RUN_START(_switch_runstart),

SIZE(_switch_size)

.text : LOAD = FLASHB, PAGE = 0 /* can be ROM */

RUN = RAMLS, PAGE = 0 /* must be CSM secured RAM */

LOAD_START(_text_loadstart),

RUN_START(_text_runstart),

SIZE(_text_size)

/* Allocate uninitalized data sections: */

.stack : > RAMM1 PAGE = 1

.ebss : > RAMGS PAGE = 1

.esysmem : > RAMGS PAGE = 1

/* Initalized sections go in Flash */

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used, */

}