- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

The following are known issues in the Code Composer Studio 4.2.4 flash plug-in for F28M35x Concerto. A patch to the plug-in is expected within the month to address these issues.

Item 1:

Subsystem(s): C28x

Issue:

Flash operations can stop working when trying to load code in secured memories. The plug-in will issue the error "Flash operation timed out waiting for the algorithm to complete. Operation cancelled."

Workaround:

Power-cycle the device.

Item 2:

Subsystem(s): M3

Issue:

The Z2 GRABSECT and GRABRAM fields are switched in the flash plug-in GUI.

Workaround:

Use the GRABSECT field to program 0x27FFE0 and GRABRAM field to program 0x27FFE4.

Item 3:

Subsystem(s): M3 and C28x

Issue:

The plugin incorrectly reports the locked/unlocked state of the device. Examples:

(a) Plugin reports that the device is already locked (when it is not really locked)

(b) Plugin report that the device is currently unlocked (when it is not really unlocked).

Workaround:

To unlock try selecting 'Lock' again before 'Unlock'.

Item 4:

Subsystem(s) M3

Issue:

Device will not unlock after programming password and performing flash operation.

Workaround:

Try reading OTPSECLOCK, GRABSECT, and GRABRAM after reset, before performing flash operations.

Item 5:

Subsystem(s): M3 and C28x

Issue:

When loading a program that writes to both Flash and RAM locations, there is a chance that the RAM data is corrupt. and the program may not execute properly.

Workaround:

After loading the program, reload using the "Load RAM Only" option in the flash plug-in.

Item 6:

Subsystem(s) M3 and C28x

Issue:

When executing a flash operation after executing code from flash, an error may occur.

Workaround:

After executing the program, perform a target reset before executing the Flash operation.

Item 7:

Subsystem(s): C28x

Issue:

If certain values are written to 0x64 and 0x65, then the Flash operations stop working. For example write 0x5555 to 0x64 and 0x65 and attempt to erase. The plug-in will respond: "Flash operation returned unsuccessfully. Operation cancelled."

Workaround:

Clear these locations before issuing a flash operation. This could be done using a gel file to write 0x0000 to these locations.

I am facing same issue as described in Item 1.

C28xx_0: Flash operation timed out waiting for the algorithm to complete. Operation cancelled.

C28xx_0: Flash Programmer: Error initializing device.

C28xx_0: Flash Programmer: Error erasing Flash memory.

I am facing same issue as described in Item 1.

The workaround for item 1 is not working for me. Can you please give me the detail steps.

M3 can be programmed with flash but only C28 is giving problem. Device is unlocked or the C28 is never got programmed using Flash. Please help.

A preliminary CCS patch with a flash plug-in update is available if you are still having issues. Note: this is still going through testing.

Download the Patch http://software-dl.ti.com/C2000/c2000_apps_public_sw/patch/CCS4.2.4.00034_update.zip

Unzip into a directory

In CCS - this patch requires CCS 4.2.4

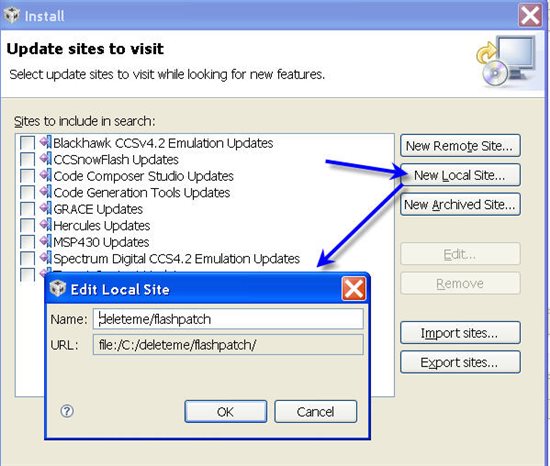

help-> Software Updates-> find and install

Select Search for New Features to Install

Add new local site

Browse to the directory where you unzipped the patch

Select "Ok"

Select all

Click Next

Accept the terms and click next

Change location if needed to your CCS 4.2.4 install and click finish

During the install: Feature Verification - warning of certificate is not recognized. Select "Install All"

When you are prompted to restart the workbench select "Yes"

The install of the patch will complete after the workbench restarts.

Vijay Nemade said:The workaround for item 1 is not working for me. Can you please give me the detail steps.

M3 can be programmed with flash but only C28 is giving problem. Device is unlocked or the C28 is never got programmed using Flash. Please help.

Please make sure the 28x subsystem is unlocked (it is a separate lock mechanism).

Regards

Lori

Hi Lori,

I installed the patch and now I can write to Flash on c28, but the program won't run, ie, I put a break point at first line of code execution and it's never hit. The project I loaded is the c28 flash example.

I have loaded both flash examples into theConcerto. The ARM side works fine, with the counters incrementing as I would expect, but c28 does not appear to run.

I have also tried the blinky projects, and don't have any issues executing code out of RAM on either core. The issue seems to be only on the c28 Flash side?

Thanks,

Tim

Hi Tim,

can you check forum post at below link for the solution to the problem you descibed above?

Best Regards

Santosh

oops missed pasting the link...

Santosh Athuru said:Hi Tim,

can you check forum post at below link for the solution to the problem you descibed above?

http://e2e.ti.com/support/microcontrollers/tms320c2000_32-bit_real-time_mcus/f/171/t/148597.aspx

Best Regards

Santosh

Hi Santosh,

I am not sure if I am seeing the same issues, but I have an issue that is similar.

I have noticed that sometimes when I run the code, it appears as if something does not get set properly, and the code does not run correctly (ex. code seems to run, but I do not get Ethernet communications with the lwIP example.) Interrupts trigger as expected, and main( ) appears to run as expected, but no comms. It appears that if I connect, disconnect, reset, unplug usb emulator cable in the right order (I haven't figure out what that order is, then things start to work correctly again.) This happens all using the same setup and code. I am guessing the culprit is in the boot ROM code, but that's just a guess.

Hope that helps a bit, and I will post more if I have additional information.

Hi Tim,

please keep an eye on the forum post link that I sent anyways.

regardign the lwip example sometimes running and sometimes not, it would be interesting to see if there is any particular sequence that makes it work always.

By the way, on the Concerto control card - when booting to flash and using EMAC from your flash application, please check the control card documentation for the information on conflict between the one of the boot mode GPIO pin and one of the EMAC pin.

Also make sure your application doesn't use any of the boot ROM reserved RAM locations as specified in the TRM - assume you must have already taken care of this. Also check for any initialization being done in your GEL scripts but not in your main, as they would be missed when operating in stand-alone mode.

yes, please let us know if you find any more information - it will be helpful to all.

Best Regards

Santosh

Hi Santosh,

I have a code set that is stable now, and I need to address an issue that I was ignoring before. I can run C28 & M3 code together in Flash when attached to the debugger. But if I detach and power cycle, both CPUs just reset at 20Hz.

Any ideas?

Tim

Hi TIm,

I assume your problem is that the code is running slower in stand-alone compared to when run from debugger? if yes,

please take a look at the last 3 or 4 posts on page 1 of this forum-discussion (http://e2e.ti.com/support/microcontrollers/tms320c2000_32-bit_real-time_mcus/f/171/t/148597.aspx) to check if it is the same issue.

I've been talking to Trey about the same and it looks like it is a flash wait states configuration issue, do you do proper flash init in the M3 flash application code? above forum link has those details explained by Harrison.

Also, if you are using SysCtlDelay function in your M3 code, have a look at this forum post link : http://e2e.ti.com/support/microcontrollers/tms320c2000_32-bit_real-time_mcus/f/171/t/152991.aspx

Let us know if above helps, the Team will be releasing an update to ControlSuite examples with all fixes very soon.

Best Regards

Santosh

Hi Santosh,

My issue is different from the ones you mentioned.

I did a compare of the gel file and mine is identical to the one posted. I am not using SysCtlDelay function.

1. When I run with debugger attached, I can get both cores to work by not executing (commented out)

master_ram_init_control_m1_msgram_memories();

master_ram_init_control_L0_L3_memories();

IPCMtoCBootControlSystem(CBROM_MTOC_BOOTMODE_BOOT_FROM_FLASH);

Of course this isn't the "correct" way to run. And I would like to have the Concerto running without being attached to the debugger.

2. If I try to execute master_ram_init_control_m1_msgram_memories(); then code hangs inside this function at the "break;" line in the function.

Tim

Hi Tim,

So, its not the issue of code running slow without debugger. You can keep the below code in your M3 application when running through debugger too, it shouldn't be a problem.

Tim11828 said:1. When I run with debugger attached, I can get both cores to work by not executing (commented out)

master_ram_init_control_m1_msgram_memories();

master_ram_init_control_L0_L3_memories();

IPCMtoCBootControlSystem(CBROM_MTOC_BOOTMODE_BOOT_FROM_FLASH);

The below status means that C-Boot ROM has not received the IPC properly or C-Boot ROM is not ready for IPC (probably because it has iTRAP exception, you can find this out by looking at CTOMIPCBOOTSTS register - sec5.6.10 and sec 5.6.11 of TRM ...boot ROM chapter could be moved to chapter 6 in latest verion of TRM, if it is then refer to section 6.6.10 and 6.6.11).

Tim11828 said:2. If I try to execute master_ram_init_control_m1_msgram_memories(); then code hangs inside this function at the "break;" line in the function.

Can you follow below steps and tell me the result:

1.> Put back the RAM-INIT code in M3 application, build and flash the application on M3

2.> load application code on C28x Flash

3.> on C28x debug window close all open Watch windows and Memory windows which read any flash address (we don't want flash to power up because of DEBUG READS from watch or memory windows)

4.> Disconnect target and terminate debug session and reset the board.

5.> Remove C28x GEL script from CCS target configuration before launching the target configuration.

6.> Launch Target configuration and connect to both M3 and C28x, do a debug reset on both the cores.

7.> Now Run C28x CPU and PAUSE it (in the disassembkly windows PC should stop at IDLE instruction, if thats not the case then you still have a memory window or watch window or GEL script which reads C28x FLASH memory, make sure that doesn't happen and repeat)

8.> if PC on C28x CPU is at IDLE instruction, then you are good - continue RUN on C28x CPU

9.> on M3 you can load your application symbols, put a break point after the RAM INIT is done and before sending the boot command to C-Boot ROM and RUN your master application.

10.> what do you see now? did it hit the break point, if it does then you are good. if it doesn't can you PAUSE and see where it is stuck and at this point please publish the value of 0x20004000 location on M3 and the value of CTOMIPCBOOTSTS location, in this post.

11> if there is no success at step 10, can you debug reset both the cores and this time RUN M3 first (set the boot mode to boot-to-flash) and then RUN C28x and see if there is any success?

if we can get a successful RUN by doing above, then your code should boot in stand-alone mode.

Best Regards

Santosh

Hi Santosh,

How should I do step 5? Do I remove it then add it back in after launching target configuration? Doesn't it need this file to initialize and set things?

Thanks,

Tim

Nope, just take it out for now. All the initializations that GEL was doing will now be done by C-Boot ROM itself and the RAM-INITs will be taken care of by M3 application MTOCIPC commands.

another easy way to remove your GEL script is just edit your GEL script and comment out everything in your GEL script, save, disconnect target, terminate debug session, reset the board and re-launch target config and connect CCS to target.

Best Regards

Santosh

Hi Santosh,

I got to step 10. It did not stop at the break point. It stopped at the same place as I mentioned before ("break".)

The value of 0x20004000 is:

And I was not able to get a value for IPC_O_CTOMIPCBOOTSTS. Also, it has not executed to that line of code.

Tim

Hi Tim,

looks like your application is loading something to 0x20004000 location and onto boot ROM reserved lcoations, so that is not helpful. But anyway we don;t have see a problem with M3 in your case so we will leave it at that for now.

you can get the value of CTOMIPCBOOTSTS location on M3 and also on C28x from the memory window. If you Pause C28x CPU where is your PC halted at in the dis-assembkly window of CCS?

CTOMBOOTSTS on M3 is at location 0x400FB740 and on C28x it is at 0x4E20.

Best Regards

santosh

Hi Santosh,

C28 stop point is below

0x004E20 on C28 is 90000. Same value for M3. I will be looking into who's loading into 0x20004000.

Tim

Hi Tim,

can you copy-paste the code on M3 where the application is waiting-for-ever?

CTOMBOOTSTS value doesn;t look good, the Lower 16bits should not be zero. Lets see.

Best Regards

Santosh

I mean can you copuy+paste your application code in this post, I would like to suggest some source code modification if possible to try out.

also, what is the input clock frequency to your device on your target?

Santosh Athuru said:Hi Tim,

can you copy-paste the code on M3 where the application is waiting-for-ever?

CTOMBOOTSTS value doesn;t look good, the Lower 16bits should not be zero. Lets see.

Best Regards

Santosh

Here it is (stops at break):

void master_ram_init_control_m1_msgram_memories()

{

unsigned int ii = 0;

//RAM INIT for M1, and CTOM MsgRAM - M0 RAM INIT is done by C-BootROM

IPCLiteMtoCSetBits_Protected( IPC_FLAG1, CCORE_M0M1_CTOM_MSG_RAM_INIT_REG_ADDR , (CCORE_M1_RAM_INIT_BIT | CCORE_CTOM_MSG_RAM_INIT_BIT) , IPC_LENGTH_32_BITS, IPC_FLAG32);

//wait until C-BootROM acks

// while(HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_FLAG1);

//CHECK IF pass or fail

if(HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_FLAG32)

{//still set - so command failed.

while(1)

{

for(ii = 0; ii < 0xDEADC0DE; ii++);

//ERROR – HAVE an ERROR INDICATOR here

}

}

//READ RAM_INIT_DONE register check

do

{

IPCLiteMtoCDataRead(IPC_FLAG1, CCORE_M0M1_CTOM_MSG_RAM_INIT_DONE_REG_ADDR, IPC_LENGTH_32_BITS, IPC_FLAG32);

//wait until C-BootROM acks

while(HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_FLAG1);

//CHECK IF pass or fail

if(HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_FLAG32)

{//still set - so command failed.

while(1)

{

for(ii = 0; ii < 0xDEADC0DE; ii++);

//ERROR – HAVE an ERROR INDICATOR here

}

}

else

{

if(HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCDATAR) & (CCORE_CTOM_MSG_RAM_INIT_DONE_BIT|CCORE_M1_RAM_INIT_DONE_BIT))

{

//RAM_INIT completed - do nothing :-)

break;

}

else

{

//RAM_INIT not done yet, so wait for more time and read ram init done register.

//GIVE some cycles delay until CCORE performs RAM INIT

for(ii =0 ; ii < 2048; ii++);

continue;

}

}

}while(1); //do-loop-end

} //function-end

Hi TIm,

what do you mean by stops at break; line?

does debugger HALT CPU when PC is at that point? are you able to pass through that point if you step-over or single step code after it stops at break?

Hitting that break means RAM-INIT is completed and everything is good.

Try re-placing that break with a return statement, so that you will return from the function and see what happens..

Best Regards

santosh

Hi Santosh,

Yes, the debugger stops at that line. I cannot pass through that line even if I try to single step. I am puzzled why it stops at such an innocuous line?

I will replace that line with a return and get back to you. If you think of anything else just let me know.

Thanks,

Tim

Hi Tim

Normally if you are single steping the M3 core and if the core locks up it is mostly because of a HARDFAULT/USAGEFAULT and which could be because of an illegal instruction or memory access, something like your are doing something very wrong (for ex: using a BLX instruction but the Rm register's bit 0 is not set, where in Rm register is the paramemter for the BLX). I haven't seen this error happen at the location in the RAM-INIT functions.

It would be worth a while to examine the disassembly window contents when this error happens. Can you Print+Scr and paste the disassembly window and source window of your CCS when this error happens?

Also, let us know if you see any different result with 'RETURN' instruction instead of a break.

Best Regards

Santosh

Hi Santosh,

As you noted, the error that you mentioned does not happen, so I'm not sure which disassembly window to print-screen. Nevertheless, I am attaching the disassembly window for when the code stops at the "break" line.

After I replaced the break statement with return, code now stops at the line just before it in the debugger (the if statement checking for RAM_INIT complete.)

Also, can you elaborate a bit more on what the register values that I provided earlier indicate? You mentioned they did not look good.

Thanks,

Tim

Hi Tim,

I was under the impression that C-Boot ROM is not able to receive any IPC so I was suspecting somehting was wrong with CTOMIPCBOOTSTS value. But it looks like your application is able to send some IPC and receive the response back -this we can tell by based on your current PC register.

in your disassembly window, I see that PC is positioned at a B instruction, I would have to dig this a bit further and I would need your entire M3 application project, can you zip it and send it to me? you have already mentioned that you see the same result even if you step through your code.

Best Regards

Santosh

Hi Santosh,

I can't zip up the entire project because it's big but since the problem I'm seeing is happening in main I can get that to you. Does that work for you, or can you narrow this down to something more specific?

Thanks,

Tim

Hi Tim,

ok, not problem, please send me your COFF file (which has the bug), MAP file, linker command file, MAIN file and your startup file that has the entry point function and the one that calls main() or the CINIT RTS library functions.

Once I get to look at those, I will ask for any further information.

Best Regards

Santosh

Also, please attach your project's clean compilation log (I believe you can copy this from your compilation status window).

Hi Tim,

Thanks for the files, I will take a look at them.

Meanwhile can you verify on your board if you are able to RUN any simple application from M3 flash which then kick starts the application in C28x flash and both the applications in master and control subsystems toggle an independent IO?

Best Regards

Santosh

Hi Tim,

good news, I was able to reproduce the error. Looks like the problem is in your code below. You have commented out the RED line below, Which you shouldn't do. Please uncomment these lines in your project and re-run the code, it should work.

What is happening here is that you application is not really waiting to check if IPCFLAG1 is cleared or not (RED LINE) but is checking for IPCFLG32. Please refer to section 6.6.12 of boot ROM chapter in TRM for details on IPCFLG1 and IPCFLG32 operations.

basically the RULE is, IPCFLG32 should be read by master only after IPCFLG1 is cleared.

Please let us know if it works with suggested changes.

void master_ram_init_control_m1_msgram_memories()

{

unsigned int ii = 0;

//RAM INIT for M1, and CTOM MsgRAM - M0 RAM INIT is done by C-BootROM

IPCLiteMtoCSetBits_Protected( IPC_FLAG1, CCORE_M0M1_CTOM_MSG_RAM_INIT_REG_ADDR , (CCORE_M1_RAM_INIT_BIT | CCORE_CTOM_MSG_RAM_INIT_BIT) , IPC_LENGTH_32_BITS, IPC_FLAG32);

//wait until C-BootROM acks

// while(HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_FLAG1);

//CHECK IF pass or fail

if(HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_FLAG32)

{//still set - so command failed.

while(1)

{

for(ii = 0; ii < 0xDEADC0DE; ii++);

//ERROR – HAVE an ERROR INDICATOR here

}

}

//READ RAM_INIT_DONE register check

do

{

IPCLiteMtoCDataRead(IPC_FLAG1, CCORE_M0M1_CTOM_MSG_RAM_INIT_DONE_REG_ADDR, IPC_LENGTH_32_BITS, IPC_FLAG32);

//wait until C-BootROM acks

while(HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_FLAG1);

//CHECK IF pass or fail

if(HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_FLAG32)

{//still set - so command failed.

while(1)

{

for(ii = 0; ii < 0xDEADC0DE; ii++);

//ERROR – HAVE an ERROR INDICATOR here

}

}

else

{

if(HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCDATAR) & (CCORE_CTOM_MSG_RAM_INIT_DONE_BIT|CCORE_M1_RAM_INIT_DONE_BIT))

{

//RAM_INIT completed - do nothing :-)

break;

}

else

{

//RAM_INIT not done yet, so wait for more time and read ram init done register.

//GIVE some cycles delay until CCORE performs RAM INIT

for(ii =0 ; ii < 2048; ii++);

continue;

}

}

}while(1); //do-loop-end

} //function-end

Hi Santosh,

I have uncommented the code line in red, reloaded, but still cannot run both cores stand alone (Flash and not attached to debugger.) Both cores does run on Flash attached to the debugger. I am double checking the system and documentation.

Tim

Hi Tim,

you should be able to boot to flash properly. Below are the steps to get both cores running from flash with debugger connected.

Can you follow below steps and tell me the result:

1.> Have the C28x RAM-INIT via IPC -code in M3 application, build and flash the application on M3

2.> load application code on C28x Flash.

3.> On C28x debug window close all open Watch windows and Memory windows which read any flash address (we don't want flash to power up because of DEBUG READS from watch or memory windows)

4.> Disconnect target and terminate debug session and reset the board.

5.> Remove C28x GEL script from CCS target configuration before launching the target configuration.

6.> Launch Target configuration and connect to both M3 and C28x, do a debug reset on both the cores.

7.> Now Run C28x CPU and PAUSE it (in the disassembkly windows PC should stop at IDLE instruction, if thats not the case then you still have a memory window or watch window or GEL script which reads C28x FLASH memory, make sure that doesn't happen and repeat)

8.> if PC on C28x CPU is at IDLE instruction, then you are good - continue RUN on C28x CPU

9.> on M3 you can load your application symbols, put a break point after the RAM INIT is done and before sending the boot command to C-Boot ROM and RUN your master application.

10.> what do you see now? did it hit the break point, if it does then you are good. if it doesn't can you PAUSE and see where it is stuck and at this point please publish the value of 0x20004000 location on M3 and the value of CTOMIPCBOOTSTS location, in this post.

11> if there is no success at step 10, can you debug reset both the cores and this time RUN M3 first (set the boot mode to boot-to-flash) and then RUN C28x and see if there is any success?

if we can get a successful RUN by doing above, then your code should boot in stand-alone mode.

Best Regards

Santosh

Santosh,

I have the same problem as above. I want the concerto control card F28M35H52C1 to work standalone, but I 'm still not able to do this after some days of work.

I started from the flash project in the control suite 2.6.1. and I did some modifications. The source files are attached. I modified the flash_c28 project that a LED is blinking in the main loop and in the flash_M3 project I added the functions you mentioned above to inint M1 RAM.

The M3 code hangs on:

//wait until C-BootROM acks

while(HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_FLAG1);

Do you have an idea whats wrong?

Thaks in advance for your answer!

Grtz 3sRol

Hello,

With the 2 functions in ipc_raminit.c, SysCtlReleaseSubSystemFromReset(SYSCTL_CONTROL_SYSTEM_RES_CNF | SYSCTL_ANALOG_SYSTEM_RES_CNF) and IPCMtoCBootControlSystem(CBROM_MTOC_BOOTMODE_BOOT_FROM_FLASH) I'm sometimes able to let the Concerto boot from flash. I load the code with CCS and reset the device by removing and adding power. By using a blinking LED, I can see that the concerto is booting. But sometimes it isn't booting...? I think the program is running in an endless loop in the RAM init functions. I don't know it exactly because I can't debug the flash code. CCS blocks after starting the flash code with the debugger and the only way to end CCS is by Ctrl+Alt+Del...

Do you have suggestions to debug the flash code? Are there known issues...? My CCS version is 4.2.5.00005.

Thanks in advance for your support!

Grtz 3s

Hi Grtz

can you give some more details on the problem.

if you are trying to run through C-Boot ROM with debugger connected, there is an Errata that you should be aware of - please refer to Control subsystem Boot ROM M0 RAM-INIT advisory in the device errata.

If you are debugging flash application on M3 and your init code on M3 is communicating with C-Boot ROM, then you have to make sure that C-Boot ROM is running properly before.

If your M3 application doesn't need C28x flash application for now, I would sugges you comment out IPCMtoCBootControlSystem() function in your M3 application.

If you M3 application is dependent on C28x flash application, then first load your C28x flash application using CCS and RUN you C28x application and on M3 application you can comment out IPCMtoCBootControlSystem() for now, until you debug your applications and RUN M3 applciation. In this case since you can get you Control subsytem application and Master application run from flash using CCS you wouldn't need the IPCBoot function and RAM-INIT(s). The control subsystem RAM-INIT is taken care of by GEL script in this case.

Now, after you are sure that both your M3 and C28x applications are running from flash properly, you need to put back the IPCMtoCBootControlSystem() on M3 and flash your M3 application.

Please be aware of above mentioned details when debugging multi-core applications.

If you need to reproduce the exact stand-alone boot behavior with emulator connected you need to exactly follow the steps listed few posts above in this thread.

Please let us know if you have any more questions.

Best Regards

Santosh

Santosh,

Santosh Athuru said:if you are trying to run through C-Boot ROM with debugger connected, there is an Errata that you should be aware of - please refer to Control subsystem Boot ROM M0 RAM-INIT advisory in the device errata.

If you are debugging flash application on M3 and your init code on M3 is communicating with C-Boot ROM, then you have to make sure that C-Boot ROM is running properly before

I'm aware of the errata, I followed the steps you discribed above to check C-boot ROM is properly running. If I disable the GEL-script, I'm able to check the C28 is running at the IDLE instruction.

Santosh Athuru said:If you M3 application is dependent on C28x flash application, then first load your C28x flash application using CCS and RUN you C28x application and on M3 application you can comment out IPCMtoCBootControlSystem() for now, until you debug your applications and RUN M3 applciation. In this case since you can get you Control subsytem application and Master application run from flash using CCS you wouldn't need the IPCBoot function and RAM-INIT(s). The control subsystem RAM-INIT is taken care of by GEL script in this case.

Thanks for this input. I commented out IPCMtoCBootControlSystem() , and if my M3 application is running from flash, and I load the C28 in RAM, everything goes well. I can debug/pauze/run... But if I load M3 in flash and C28 in flash, start a debug session, connect both cores, load .out file in both cores, the debugger/CCS freezes completely (Sometimes immidiately after loading C28, sometimes only after clicking a button). The only thing I can do is Ctrl+Alt+Del and force to stop CCS.

If I uncomment SysCtlReleaseSubSystemFromReset(), IPCMtoCBootControlSystem() and the 2 RAM Init functions in M3 application, rebuild M3, start a debug session, connect both cores, load .out file in both cores, the debugger/CCS freezes again. The only difference I have is that, after a power reset, the Concerto is booting well from flash, an on the first point, it looks all functionality is OK. But I have to check this more in detail.

Are the 11 points listed above the correct way to debug a flash application?

Thanks in advance for your support!

Grtz 3s

Hi Grtz

3sRol said:if my M3 application is running from flash, and I load the C28 in RAM, everything goes well. I can debug/pauze/run... But if I load M3 in flash and C28 in flash, start a debug session, connect both cores, load .out file in both cores, the debugger/CCS freezes completely (Sometimes immidiately after loading C28, sometimes only after clicking a button). The only thing I can do is Ctrl+Alt+Del and force to stop CCS.

If I uncomment SysCtlReleaseSubSystemFromReset(), IPCMtoCBootControlSystem() and the 2 RAM Init functions in M3 application, rebuild M3, start a debug session, connect both cores, load .out file in both cores, the debugger/CCS freezes again. The only difference I have is that, after a power reset, the Concerto is booting well from flash, an on the first point, it looks all functionality is OK. But I have to check this more in detail.

For the above, I hope that you are able to load the out files to flash correctly. Once you are sure that C28x flash and M3 flash are programmed correctly (No CCS hangs or any other errors) - now you are ready to debug your applications in flash.

Now your M3 application is coded to send a Boot mode IPC command (and RAM-INIT related IPC commands) to C-Boot ROM on start up. So you will have to have C-Boot ROM in running in good condition to be able to process this IPC. which means you will have to RUN C-Boot ROM now and since your debugger is connected and you have to RUN C-Boot ROM, you should comment out the below shown lines (in RED) in the C28x GEL script, disconnect target and terminate debug session. Now reset the target and launch your debug session and connect to both the cores and do a debug reset.

OnReset(int nErrorCode)

{

C28x_Mode();

// Unlock_CSM();

// Unlock_ECSL();

// ReadFlashEXE();

C28x_Disable_Flash_ECC();

}

Keep the above commented as long as your debug session needs to RUN C-Boot ROM. If you don;t have to run C-Boot ROM but simply load and RUN your application from C28x flash or RAM then uncomment the lines from the C28x GEL script.

Once you have everything else connected and now since you have alreay programmed M3 and C28x flash with your application, just load symbols_only and do a debug reset on both cores.

Run, C28x and then Run M3 ( set the boot mode switches to boot to flash on M3) - both your applications should be running.

Note that after you load symbols_only this time, you can set break points at functions in your M3 and C28x application as usual and do a debug reset and run C28x and M3. If your application is written properly it doesn't matter which core your run first. But let me know if above works for you.

and yes, the 11 steps listed in posts above should help debug your applcations in flash, but at step 5, instead of removing entire GEL script you can comment the above lines and still keep the C28x GEL script.

Best Regards

Santosh

Hi Grtz

nice...happy concerto days. Feel free to post any findings, comments, suggestions and questions you have.

Best Regards

Santosh