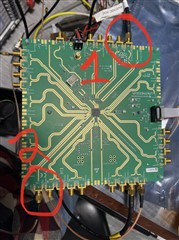

Part Number: LMK04832EVM

Other Parts Discussed in Thread: LMK04832, LMK04610, LMK03318

Hello,

First a little background:

I have your LMK04832EVM board hooked up to a Keysight DSO404A oscilloscope. I see an output on the CLKout I have selected however there is an offset from the frequency selected on the GUI (TICS Pro) and the frequency observed on the oscilloscope (about 30MHz).

When I switch the VCO_MUX to CLKin1 and provide an external clock the board I observe the clock buffer (perhaps its the divided external signal frequency) as opposed to what I want to see which is the selected frequency on CLKout.

Also I need help setting up an external SYNC clock. I'm using an external reference clock at 122.88MHz. The LED for PLL2 is on indicating a lock however the LED for PLL1 is not on and I'm not sure why that is or if that indicates an issue.

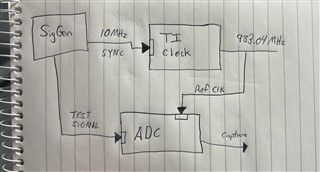

What I'm trying to achieve:

My goal is to have two CLKout's, one at 980MHz and one at 10MHz while using the external sync.

If you could share screenshots of the TICS Pro GUI on how to achieve this setup that would be most useful.

Kind Regards,

Alex