Other Parts Discussed in Thread: DRV8881, DRV8426

Hi,

A customer asked me about the results of the short-circuit test.

Waveforms and questions are included in the attached document, so could you please comment?

Best Regards,

Nishie

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Nishie-san,

Please see section 7.3.8.3 of the datasheet. This explains there is an analog current limit on a short-circuit event that attempts to reduce the current before a OCP event occurs after Iocp deglitch. This is different from Itrip....I don't believe that Itrip is happening.

Also, is the fault LATCHED? If latched, customer would have to cycle nSLEEP or device power to recover. If it is latched, than can only be OCP or OTSD. Sometimes it is hard to determine in OTSD as temperature rises very quickly on the die itself and camera is not fast enough to pick up change or thermocouple is also not fast enough.

Regards,

Ryan

Hi Ryan-san,

Thank you for your reply.

I have additional questions.

1. I think that the current limit you mentioned is as follows in the relevant part of the data sheet. Is this right?

"An analog current-limit circuit on each FET limits the current through the FET by removing the gate drive."

2. If yes, does it mean that there is a current limiting circuit in addition to the Itrip circuit and OCP circuit?

3. If No, I don't understand the factors that limit the current within the blanking time at all, so please give me a detailed explanation.

Best Regards,

Nishie

Hi Ryan-san,

Current limiting is part of OCP block. It is different than Itrip circuit.

->OK, we would like to confirm “Current limiting is part of OCP block.”.

-There is current limit circuit on OCP block apart from Itrip circuit.

-We recognize that the conventional stepping motor driver(like as DRV8881) doesn’t have current limit circuit on OCP block.

Does DRV8426 add this as the brand new function?

Furthermore, do DRV84 series products have the same function also?

-There is no detail description of current limit circuit on OCP block at the datasheet.

Could you let us know followings?

1. How much is upper current limit? On our customer’s wave form, it seems that current limit is 7.4A.

2. How much is blanking time of upper current limit? Nothing?

3. If there is current limit circuit on OCP block, are wave forms which we attached expected behavior?

Best Regards,

Nishie

Nishie-san,

This block is quite common. You can check DRV8881 datasheet...same description is there. It is not new and entire DRV84xx family shares this operation.

1) Current limit starts when current is > Iocp. Current will continue to rise until Rdson increases as part of limiting the gate drive. It will then begin to fall.

2) There is no blanking time on this feature.

3) This is expected behavior. Device will protect itself as you see.

Regards,

Ryan

Hi Ryan-san,

OK, we got current limit circuit on OCP block.

We got that Waveform1 which we attached is expected behavior.

However, we would like to confirm Waveform2.

There is the difference between Waveform1 and Waveform2 in spite of the same short conditions.

In case of Waveform2, compared with Waveform1, it seems that current falls rapidly.

Is it relation to following your comment?

“Current will continue to rise until Rdson increases as part of limiting the gate drive. It will then begin to fall. “

If it not have any relation of Rdson increasing, do you have any advice for it?

For example : during Toff with the slow decay mode, it occurs short event, it might this problem,,,

Then, you mentioned followings;

“Also, is the fault LATCHED? If latched, customer would have to cycle nSLEEP or device power to recover. If it is latched, than can only be OCP or OTSD. Sometimes it is hard to determine in OTSD as temperature rises very quickly on the die itself and camera is not fast enough to pick up change or thermocouple is also not fast enough.”

->The customer checked the fault LATCHED. Therefore the fault can only be OCP or OTSD.

About OTSD, the customer checked the device with their hand, however there is no hot.

Especially, we would like to know why Waveform2 cause of.

Best Regards,

Nishie

Nishie-san,

In waveform 2, it appears that in CH3 (AOUT2), the low-side is switching on. In waveform 1, the output is staying high and high-current condition continues. I forgot to ask before, but this is an OUTPUT-to-OUTPUT short? I think so.

It is possible to hit Itrip before Iocp under some conditions. Especially if there is inductance in the short or the short is applied at the end of a long cable (with inductance). This will slow down the current rise just long enough to have Itrip before Iocp. They are seperate circuits as explained before. If Itrip happens, slow decay mode can occur and both outputs will go to LOW state. This will reduce the current more quickly.

I believe that is what is going on in waveform 2 case.

Regards,

Ryan

Hi Ryan-san,

Thank you for your reply.

It is possible to hit Itrip before Iocp under some conditions.

->On the waveform2, the current limits within 100ns.

Itrip has blanking time = 1.0us.

Then, Blanking time starts to count after the outputs change states.(Refer to following URL.)

“Also whenever the outputs change states. Blanking time is intended to avoid false over-current events during state changes."

Might Blanking time be shorter depending on the output conditions?

Also, it seems that nFault asserted. Are Itrip and OCP detected on the same timing?

Best Regards,

Nishie

Nishie-san,

Can you tell me what the input state is when this short is applied...same for both waveforms?

1). Is the motor moving and short applied? Same condition for waveform #1/#2?

2) Is motor loaded?

3) What is the DECAY mode?

4) What is VREF?

5) Is the same behavior observed on B channel?

Is waveform #2 repeatable? Is short applied in waveform #2 soon after short applied in waveform #1? Or is there a long time between short conditions? How is the fault cleared between shorts? nSLEEP cycled or power cycled?

Regards,

Ryan

Hi Ryan-san,

Can you tell me what the input state is when this short is applied...same for both waveforms?

1). Is the motor moving and short applied?

>No.

Same condition for waveform #1/#2?

>Yes.

2) Is motor loaded?

>NO.

3) What is the DECAY mode?

>Smart tune Ripple Control

4) What is VREF?

>VREFA=0.05V~0.1V

5) Is the same behavior observed on B channel?

>The same phenomenon happened on channel B

Is waveform #2 repeatable? Is short applied in waveform #2 soon after short applied in waveform #1?

>Yes.

Or is there a long time between short conditions?

>Yes

How is the fault cleared between shorts? nSLEEP cycled or power cycled?

>After releasing the latch of nFAULT, the SLEEP pin is operated to restore it.

(The same result was obtained even if the power was turned on / off.)

Best Regards,

Nishie

Nishie-san,

Not sure how to explain this without understanding input conditions and if the device is going into start of current regulation when short is applied. Device survives every short? If so, then what is the customer concern?

Regards,

Ryan

Hi Ryan-san,

Customer concerns regarding Waveform # 2 are:

・Reason for asserting nFault

・Clamping in a short time is different from waveform # 1, but can it be considered to be due to the current limiting circuit of OCP?

Best Regards,

Nishie

Nishie-san,

If they wait a longer period of time between first short and consecutive shorts, do they still get a waveform similar to #2 or does every short look like #1? I would like to see if they could wait 30 seconds or even a minute between shorts . This would allow the device to cool between shorts and this would help me better understand if thermal protection is playing a role here.

Regards,

Ryan

Ryan san

Thank you for your cooperation always!

I work with Nishie san.

We got the wave forms which you requested.

Please refer to the attachment file.

20220510_DRV8426.pdf

Kind regards,

Hirotaka Matsumoto

Matsumoto-san,

Thank you! Seems not related to thermal. What are the state of the inputs during these shorting events? Are they transitioning at all or held at a steady state? If held at a steady state, what are the voltages on each input pin?

Regards,

Ryan

Ryan san

Thank you for your reply.

What are the state of the inputs during these shorting events?

Are they transitioning at all or held at a steady state? If held at a steady state, what are the voltages on each input pin?

->We heard that they keeps the same input conditions, we will confirm it again.

And then, we will reguest the customer get the waveform.

As the reference, the customer has gotten input condtions before short tests.

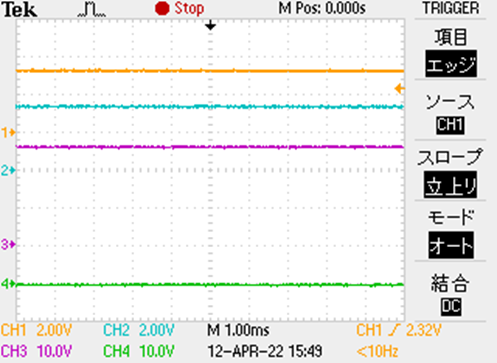

(Please refer to the wave form.)

CH1=AEN, CH2=APH, CH3=AOUT1, CH4=AOUT2

Kind regards,

Hirotaka Matsumoto

Ryan san

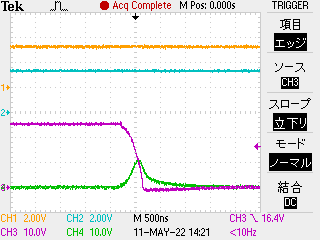

We attach the waveform which the customer captured inputs conditions during short test.

(CH1=AEN, CH2=APH, CH3=AOUT1, CH4=AOUT2)

It seems that inputs are not noisy, and these signals are steady state 3.3V.

Kind regards,

Hirotaka Matsumoto

Hi All,

I would check if differences in turning off behaviour are not caused by switch that performs short circuit. I would check voltage waveforms directly on both contacts of the switch, after short starts they both should stay the same. If the switch is of mechanical type then contacts bouncing may happen, though it usually lasts single milliseconds not microseconds.

Best Regards,

Grzegorz

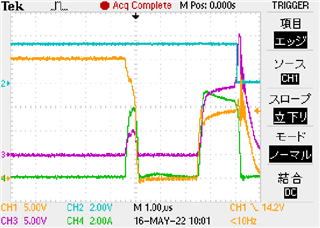

Hi Crzegorz-san and Ryan-san,

The waveforms posted so far have a test pin connected to the OUT terminal of the device on the customer's board, and a short-circuit test was performed by contacting the lead wire with this test pin.

In addition, the waveform when the short-circuit test was performed using the mechanical switch is attached.

I don't think there is any impact from chattering, but I would appreciate any comments.

Ch1: AOUT1, Ch2:nFAULT, Ch3:AOUT3, Ch4:Short current

Ch1:Both ends of the mechanical switch, Ch2:nFAULT, Ch4:Short current

Best Regards,

Nishie

Nishie-san,

I really have no explanation for this. CH1 looks like it is being pulled to GND (or near GND) and then spontaneously recovers after ~2.5us. Current rises back up and a fault occurs. I checked some previous plots and it seems that VM and VCP are stable. Is VCP measured differentially with respect to VM? If VCP collapses, that could explain why the high-side is collapsing.

Regards,

Ryan

Hi Nishie-san,

I agree with you, chattering/ contacts bouncing probably does not cause the switching differences, after short is made AOUT1 and AOUT3 stays at the same level (the first of the last waveforms you sent) .

Looking at longer current waveforms we can see that they last around 1.6-2us what would suggest current is turned off by OCP circuit with OCP deglitch time 1.8us. At the time of current negative slope significant ringing occurs at AOUT terminals what would suggest current is turned off quickly during fast decay caused by turning all Mosfets off by OCP circuit.

Looking at shorter current waveforms we can see that most of them decay slowly at the beginning with no ringing, I think that part is caused by Itrip circuit with slow decay mode. After 1.5-2us current starts to decay faster causing ringing, that part can be caused by OCP circuit with fast asynchronous decay. I guess Itrip circuit can switch current off without additional delay (1us blanking time) if APH and AEN terminals have been ON long enough before short occurs. I can not explain time between short and long current waveforms that is around 2.5us instead of 7us minimum (PWM off-time).

Making short circuit tests with different TOFF time and DECAY settings might help to better understand switching off process and check if what I said may be true.

All above are just my thoughts, I do not have experience with DRV8426 and I may be wrong.

Best Regards,

Grzegorz

Hi Grzegorz-san,

Thank you for your advice.

Hi Ryan-san,

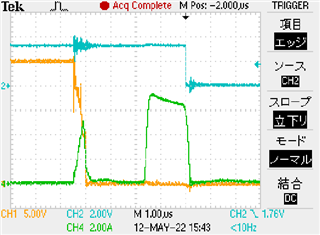

The customer measured the waveform under the following conditions.

① After shorting the output, the input signal (APH, AEN) is changed from Low to High.

-Ripple control decay

② After setting the input signal to High, short the output.

-Mixed decay

-Toff = 7us

③ After setting the input signal to High, short the output.

-Mixed decay

-Toff = 32us

Each test was performed 5 times in a row, and similar waveforms were obtained.

From these data, "If APH / AEN is not constantly changing in the H state, there is no blanking time for Itrip, so when it hits the Trip current, it is in operation to enter Decay control.” Is the recognition correct?

Best Regards,

Nishie

Nishie-san,

Thank you! Good clues, but I am confused by your statement underlined below. Can you please add more words to help me understand?

If APH / AEN is not constantly changing in the H state, there is no blanking time for Itrip, so when it hits the Trip current, it is in operation to enter Decay control

Regards,

Ryan

Hi Ryan-san,

Sorry for the lack of explanation.

We have created materials about the test conditions and the short test that was conducted.

I would appreciate it if you could check the attached file and comment.

Best Regards,

Nishie

Nishie-san,

I believe that Grzegorz-san provided the missing piece to this puzzle!! A month ago, we both guessed it was Itrip (scroll up about 1 month ago) as it appeared the device was going into slow decay.

What I didn't think about was the blanking time with static inputs. That is the piece that Grzegorz-san provided and the debug to get there was a good suggestion.

I think your presentation is perfect. Please close this case with the customer.

Regards,

Ryan

Hi Nishie-san,

You are welcome. I am glad to hear you were able to solve the problem.

Best Regards,

Grzegorz