航空宇宙/防衛システム、試験/計測機器、車載LIDARアナログ・フロントエンド(AFE)など、最新の高速データ・コンバータを使用したハードウェアの設計では、高周波数の入力、出力、クロック・レート、デジタル・インターフェイスなどに関して困難な課題に直面します。主な問題としては、FPGA(フィールド・プログラマブル・ゲート・アレイ)との接続、最初の設計パスを確実に機能させること、構築前のシステムの最適なモデリング方法の決定、などがあります。

この記事では、それらの各課題について詳しく見ていきます。

迅速なシステム開発

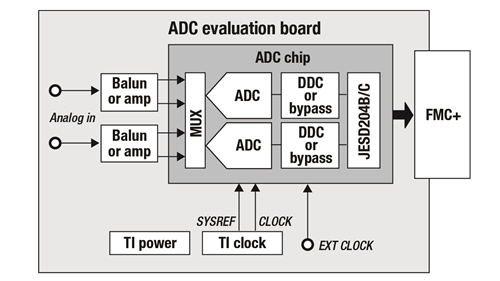

新しいハードウェア設計を開始する前に、エンジニアは多くの場合、最も重要なチップを自身のテスト・ベンチで評価します。標準的な評価基板を動作させるのに必要な機器を用意したら、通常は非常に理想的な電源と信号源に使用して、コンポーネントの評価を行います。TIがほとんどの場合に行ってきたことは、最小限のテスト・ベンチ機器と、より理想的な電源や信号源で基板の動作を開始できるように、オンボードの電源とクロックを提供することです。そのような構成の例を図1に示します。

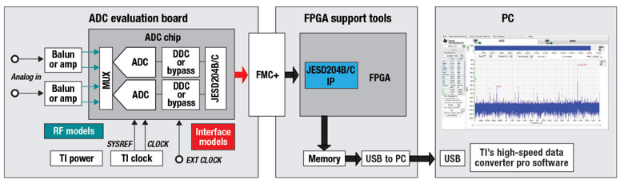

性能を検証し終えたら、サブシステム内の該当部分に対するリファレンス・デザインとして、より包括的な評価基板の回路図とレイアウトを使用できます。TIのデータ・キャプチャおよびパターン生成ツールは、CMOS、LVDS、JESD204をサポートし、それらの操作に必要なソフトウェアが付属しています。高速データ・コンバータ用の評価基板ユーザー・ガイドを使用すれば、ほとんどの基板を10分以内に動作させることが可能です。図2をご覧ください。

図2:TIのデータ・キャプチャおよびパターン生成ハードウェアとソフトウェア

図2:TIのデータ・キャプチャおよびパターン生成ハードウェアとソフトウェア

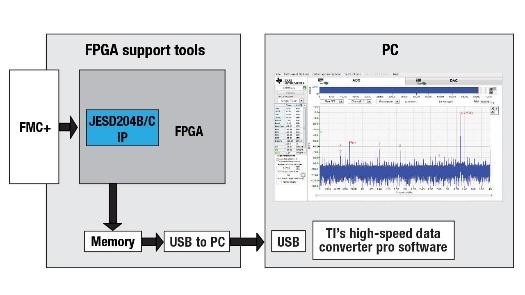

システムが複雑になるにつれて、より広い範囲のユースケースでの評価が必要になる場合があります。それには評価基板が役立ちます。評価のニーズが複雑になる場合には、Python、Matlab、Labview、またはC++ソフトウェアを使用し、デバイスの評価基板、キャプチャ・カード・ソリューション、およびテスト・ベンチ機器を介して、デバイスと直接通信できます。TIのサポート基板の優れた例としては、LVDS/CMOS用の『TSW1400EVM』、またはJESD204Bシリアライザ-デシリアライザ(SerDes)プロトコル・デバイスをサポートする『TSW14J56EVM』などがあります(図3を参照)。

図3:JESD204Bデータ・キャプチャおよびパターン生成用のTIの評価基板『TSW14J56EVM』

図3:JESD204Bデータ・キャプチャおよびパターン生成用のTIの評価基板『TSW14J56EVM』

TIでは、単一のPCから、マルチ評価モジュール・プロトタイプの包括的なシステム・レベル・モックアップをサポートしています。例えば、KCU105やVCU118などのXilinx FPGA開発キットを複数のA/Dコンバータ(ADC)またはD/Aコンバータ(DAC)に接続することで、送信および受信チャネルを同時にテストすることが可能です。

コンセプトからプロトタイプまで、デザインを加速

FPGA接続とJESD204BおよびJESD204C

最も大きな問題の1つは、FPGAとの間でどのようにデータをやり取りするかです。LVDSおよびCMOSは単純なインターフェイスですが、デバイスのピン単位でサポートできる速度が非常に制限されています。新しい高速データ・コンバータは一般に1GSPSを超える入力または出力レートをサポートしているため、これらのインターフェイスは処理が追い付かないか、設計がそれほど単純ではなくなります。

マイクロエレクトロニクス業界向けのオープン規格を開発しているJEDECでは、12.5Gbpsを超える差動ペア・レーン・レートをサポートしてこの問題を解決するために、JESD204を作成しました。しかし、JESD204はピン数を最小限に抑える一方で、パラレル・データをエンコードしてシリアライズする(またはデシリアライズしてデコードする)ことにより、インターフェイスの複雑さを増します。

これまでは、主にJESD204の知的財産(IP)ブロックと、FPGAベンダーによって提供されるサポートに頼る必要がありました。これらのIPブロックは非常によく機能しますが、任意の構成で任意のデバイスをサポートできるように提供されています。これは、特定のユースケースに対して学習し構成することが難しくなることを意味します。多くの手間をかけて独自にIPを設計するか、サードパーティのIPプロバイダからIPを入手するかのいずれかが必要になります。ただし、サードパーティのIPでは、問題が起きた場合の支援やサポートが実装時に必要となります。

TI独自のJESD204高速設計IPは、事前に構成可能で、特定のFPGAプラットフォーム、データ・コンバータ、およびJESD204モードに対して固有の最適化が可能です。TIのIPは、必要なFPGAリソースが少なくて済み、特定の各用途に向けてカスタマイズもできます。もう1つの利点は、JESD204リンクの実装に従来のような数週間や数か月ではなく、数時間または数日しかかからないことです。

FPGAプラットフォーム、データ・コンバータおよびJESD204モード向けに、JESD204 Rapid Design IPは事前構成および最適化が可能です。このIPは、特定の用途ごとにカスタマイズされていながらも、より少ないFPGAリソースで済みます。もう一つの利点は、JESD204リンクの実装に数週間から数か月かかっていたのが、数時間または数日で完了します。

デバイス・モデル

高速データ・コンバータととともに、直接の無線周波数(RF)サンプリングや非常に高速なSerDesが一般化する中で、RFとシグナル・インテグリティをモデル化する能力が、最初のパスで設計を成功させるために必要となっています。従来、ほとんどのベンダーは、Sパラメータ・モデルでADCの入力インピーダンス情報のみを提供していましたが、TIの『ADC12DJ3200』、『ADC12DJ5200RF』、および『ADC12QJ1600-Q1』高周波入力デバイスは、最大8GHzのサンプリング周波数に対応し、インピーダンスと周波数応答の情報を含むSパラメータ・モデルを有しています。

この新しいモデルにより、期待されるデバイス動作をシミュレートし、インピーダンスのマッチングを最適化できます。TIの戦略は、インピーダンスのマッチングと目的の周波数応答の実現がより困難になるような、非常に高い入力および出力周波数をサポートするデバイスに、これらのモデルを提供することです。

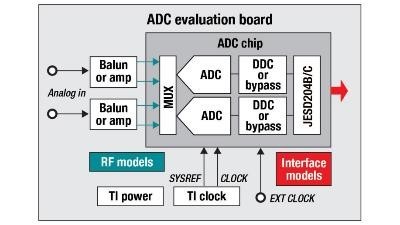

データ・コンバータのデジタル・インターフェイス側では、IBIS(Input/Output Buffer Information Specification)が一般的なモデルであり、CMOSおよびLVDSピンの物理的なレイヤ情報に加え、DCタイプとACタイプの動作の情報を提供します。高速JESD204 SerDesを使用した新しいデータ・コンバータのほとんどで、これらのモデルはIBIS-AMI(Algorithmic Modeling Interface)へと強化され、これにはイコライゼーションやプリ/ポスト・エンファシスを適用する際に役立つ情報が含まれています。IBIS-AMIは、良好なビット・エラー率、シグナル・インテグリティ、堅牢なデータ・リンクを実現しながら、基板の設計を最初から成功させるために必要なモデリングを提供します。図4に、RFモデル(緑色)とデジタル・インターフェイス・モデル(青色)を示します。

まとめ

高速データ・コンバータを使った設計に長く携わっている方々も、または高速設計を始めてから比較的日が浅い方々も、TIがそれを使いやすくしているという事実を知れば安心できるかもしれません。TIでは、図5に示すように、これらすべてを簡単にするために包括的な開発環境を構築しています。

容易なFPGA統合のためのすぐに使えるIPに加え、高精度のRFシステム・モデルと、市場で最も堅実な、柔軟性が高くスケーラブルで自動化可能な一連の評価モジュールにより、ファームウェアの開発時間を数か月短縮し、コストのかかる設計サイクルを削減し、概念からプロトタイプまでの高速設計をさらに加速することができます。

参考情報:

+高速データ・コンバータ・プロ・ソフトウェア

+トレーニング・ビデオ:High-Speed Analog-to-Digital Converter (ADC) Fundamentals(英語)

+アプリケーション・レポート:System Design Considerations when Upgrading from JESD204B to JESD204C(英語)

+技術記事:So, what are S-parameters anyway?(英語)

※すべての登録商標および商標はそれぞれの所有者に帰属します。

※上記の記事はこちらの技術記事(2020年10月13日)より翻訳転載されました。

※ご質問はE2E Support Forumにお願い致します。