作者:德州儀器應用工程師 John Wallace

多功率金屬氧化物半導體場效應電晶體(MOSFET)使用一層薄薄的氧化物作為絕緣層,分隔閘極與電晶體的主動區域。如同用於製造微處理器的MOSFET元件,功率MOSFET的閘極氧化層也非常容易因靜電放電(ESD,electrostatic discharge)而損壞。ESD可能造成閘極氧化物崩潰等嚴重故障,或元件輕度毀損。

部分離散式功率MOSFET與電源塊MOSFET (power-block MOSFET)整合 ESD保護結構,能避免ESD造成MOSFET意外故障。本文主要說明用於功率MOSFET之不同ESD防護類型,探討這類元件的設計考量。

TI MOSFET採用的ESD結構

離散式功率MOSFET與電源塊MOSFET的ESD保護可分為三大類:無ESD保護、單端ESD保護以及背對背ESD保護。

無ESD保護

顧名思義,這一類並無ESD防護,也是TI與其他製造商多數功率MOSFET與電源塊MOSFET產品的主要類型。雖然這類MOSFET無整合閘極ESD結構,但仍具有低至150V、高達3,000V的ESD耐受能力。ESD耐受能力與元件密度與電荷有關,亦即晶粒尺寸越大,耐受能力也越高。

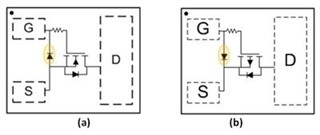

設計人員應確保MOSFET的ESD耐受能力滿足應用所需,並視需要增添外部ESD保護元件。圖一為 TI無整合 ESD 保護之 N 通道與 P 通道 MOSFET 的電路圖。

圖一:無ESD保護的MOSFET:(a) N通道與(b) P通道

單端ESD保護

第二類為配備閘極至源極單端ESD保護二極體的N通道與P通道MOSFET。此類元件的ESD額定值可達4,000V以上。功率MOSFET閘極的ESD保護多半會造成閘極漏電流增加,但是部分元件,如TI 的CSD25480F3,目前可實現低至25nA的漏電流,為業界領先規格,性能甚至比無閘極ESD保護的元件更好。

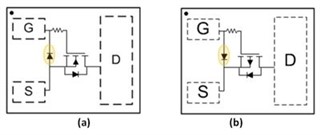

在電池應用中,備用電源與運行時間極為重要,而TI的MOSFET閘極漏電流低,是非常適合的選擇。設計人員須謹慎評估操作條件,確保ESD二極體並非處於順向偏壓,否則會產生導通情形。若無法避免順向偏壓(forward bias),建議在電路中配置限流之外部閘極電阻。圖二為 N 通道與 P 通道電路圖,並特別標示出單端ESD保護二極體。

圖二:具有單端ESD保護之MOSFET:(a) N通道與(b) P通道

背對背ESD保護

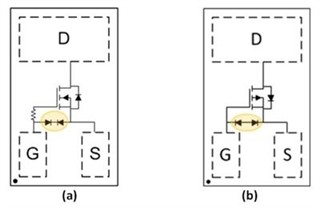

最後一類為具有背對背 ESD 保護結構之 N 通道與 P 通道 MOSFET。這類元件的ESD耐受能力為400V至3,250V不等。在背靠背的ESD結構中,無須擔心順向偏壓的問題,但此類MOSFET的閘極漏電流高於具有單端ESD保護之MOSFET,在電池應用中可能是一項缺點。圖三顯示N通道與P通道電路圖,並特別標示出背靠背ESD保護元件。

圖三:具有背靠背ESD保護之MOSFET:(a) N通道與(b) P通道

TI MOSFET產品之ESD額定值與漏電流

表一針對TI各類N通道與P通道MOSFET,列出在人體放電模式(HBM,human body model)與充電裝置模式(CDM,charged device model)下的ESD額定值與閘極漏電流最大值。

|

零件編號 |

N/P通道 |

ESD保護類別 |

HBM ESD額定值(V) |

CDM ESD額定值(V) |

IGSS最大值(nA) |

|

N |

無 |

600 |

2,000 |

100 |

|

|

P |

無 |

250 |

1,500 |

-100 |

|

|

N |

單端 |

7,000 |

2,000 |

50 |

|

|

P |

單端 |

4,000 |

1,000 |

-50 |

|

|

N |

背對背 |

3,000 |

2,000 |

5,000 |

|

|

P |

背對背 |

2,000 |

2,000 |

10,000 |

表一:具有各類ESD保護之TI MOSFET額定值

總結

離散式功率MOSFET與電源塊MOSFET提供不同的閘極ESD保護,各類提供的ESD防護等級與產生的閘極漏電流也不盡相同、各有優缺。設計人員若能了解這些特性,便能在為應用選擇MOSFET時,做出最適合的選擇。

建議在閱讀 TI MOSFET 與電源塊產品規格表時,不妨瀏覽第一頁的電路示意圖,了解元件所含的ESD保護類型。

其他資源

- TI MOSFET支援與訓練中心

- 閱讀應用報告《靜電放電(ESD)》