德州儀器作者: Izak Walker

比較器是幾乎所有應用都會出現的基本類比元件。描述比較器有此一說,視之為 1 位元類比轉數位轉換器(1-bit ADC):有兩個輸入,一個通常用作電壓參考,另一個用作輸入電壓訊號。依據作為參考的輸入為何,以及輸入電壓為何,比較器輸出會高低切換。這些元件有很多用途,特別是在混合訊號和控制應用,例如過電壓和欠電壓檢測以及溫度感測。

比較器的概念很簡單,但在使用過程中還是有幾個設計挑戰十分常見。為了應付這些挑戰,我們將透過一系列三篇文章,探討設計師為了追求比較器最佳效能而必須處理的三大常見設計考量,本文是第一篇—從「顫振」談起。

什麼是「顫振」?

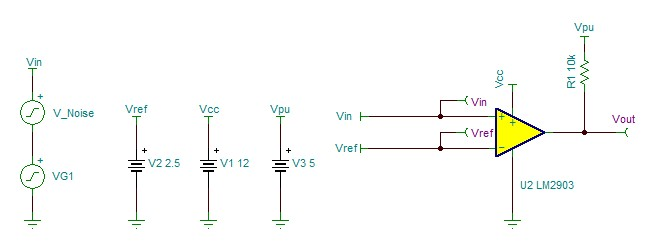

為了清楚說明顫振現象,我在非反相配置中設置了 LM2903 雙路差分比較器(dual differential comparator)(圖 1),把雜訊添加到以參考電壓 (VREF) 為中心的 1V 峰對峰值三角波中。當輸入電壓 (VIN) 接近 IN– 上的參考電壓,會出現多次快速轉換,如圖 2 所示。

圖 1:非反相比較器配置

圖 2:比較器顫振

這些快速轉換有時會被誤認為「振盪」;然而,這種表現實際上被稱為「顫振」。 「顫振」不代表設備存在缺陷;這是正常的。從比較器的觀點來看,訊號在參考閾值上上下下。參考值附近即使是非常輕微的變化,也會造成輸出的狀態轉換。比較器具有相對快的反應時間,並且只要訊號變化在其最大觸發頻率內就會改變狀態。

顫振的原因與影響

顫振的主要原因是系統中存在的雜訊,可能有多個來源,包括輸入、VREF、電源、組件、原型板—甚至比較器本身。若比較器輸入綁在一起,內部偏移電壓 (VOS¬)大約為 0 mV時,光是比較器的雜訊就可能會引起顫振。無論雜訊來源為何,比較器的輸出都會出現顫振,因為輸入電壓會快速隨機而連續地在參考值上下振顫。

輸出的顫振如果沒有檢查出來,會是嚴重的問題。不需要的輸出狀態轉換,可能會造成 FET 開關等下游設備的錯誤訊息和控制,導致不穩定的系統行為,可能使系統失去作用。例如,顫振會導致控制 DC/DC 轉換器觸發針腳的比較器反覆充電而關閉系統。此外,例如電池電壓或溫度傳感測器電壓這種移動慢的訊號,更容易受到顫振影響,因為訊號會慢慢地越過參考電壓,雜訊因而可能招致更多參考電壓交越。這可能會無意中啟動和停用欠電壓或過電壓,以及熱保護電路。

顫振解決方案

對抗顫振主要有兩種方式,都有次要的子選項。第一種選項是透過正回饋實現外部遲滯,有效地增加了高於和低於參考電壓的偏移電壓閾值。圖 3是一組採非反相配置外部遲滯的比較器及其傳遞特性曲線。

圖3:非反相配置外部遲滯的比較器

消除顫振的另一種方法,是使用例如 TLV7012這樣採整合或可變遲滯(variable hysteresis)的比較器。相關資料表規格請參見圖 4。在空間緊縮的印刷電路板上,整合遲滯還有節省空間的好處,因為可以在佈線圖中移除某些元件。

圖 4:TLV7012 遲滯規格

舉例來說,TLV3603 和 TLV3605 有一個針腳提供可調節的內部遲滯。 LE/HYS 針腳(見圖 5)能依據針腳和射極電源電壓 (VEE) 之間連結的電阻值,啟動可變遲滯,而減小電阻會增加遲滯到一定程度。如果晶片提供的遲滯不足(大於系統中存在的雜訊),仍然可以執行外部遲滯。

圖 5:VHYST (毫伏) vs. RHYST (k歐姆)

對於很重視直流準確度的高速系統來說,使用回饋電容器、而非電阻器來進行短期遲滯,可以在不影響閾值電壓的情況下做到交流遲滯。之後將另有一篇專文擴大探討交流遲滯的概念。

減少顫振可能性的第二個選擇,是過濾輸入訊號、參考訊號或兩者皆進行。適當地繞過電源,也有助於最大程度地減少大型電流尖峰引起的故障。過濾輸入的缺點,是它會延遲訊號,並且可能違反嚴格的系統時序要求。然而,藉由過濾輸入消除顫振而不改變電壓閾值狀態轉換,這是可能的。

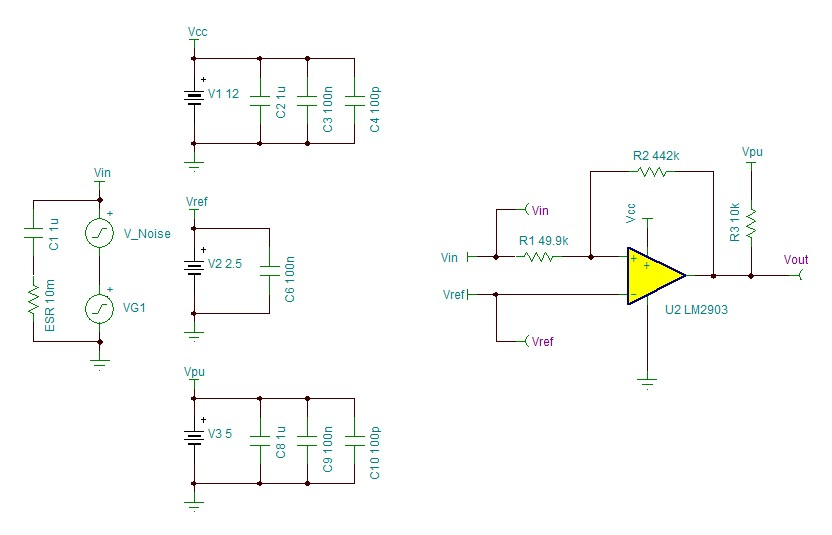

圖 6 顯示了一種可能的濾波方案,結合遲滯來消除下方顫振。請注意在佈局允許的情況下,我建議盡可能靠近針腳放置旁路或濾波電容器,達成最大效用。在不同的十進制範圍(例如,1 µF、100 nF 和 100 pf)中使用多個旁路電容器,可以跨頻率範圍提供最佳的降噪效果。

圖6:採外部遲滯和濾波的非反相比較器

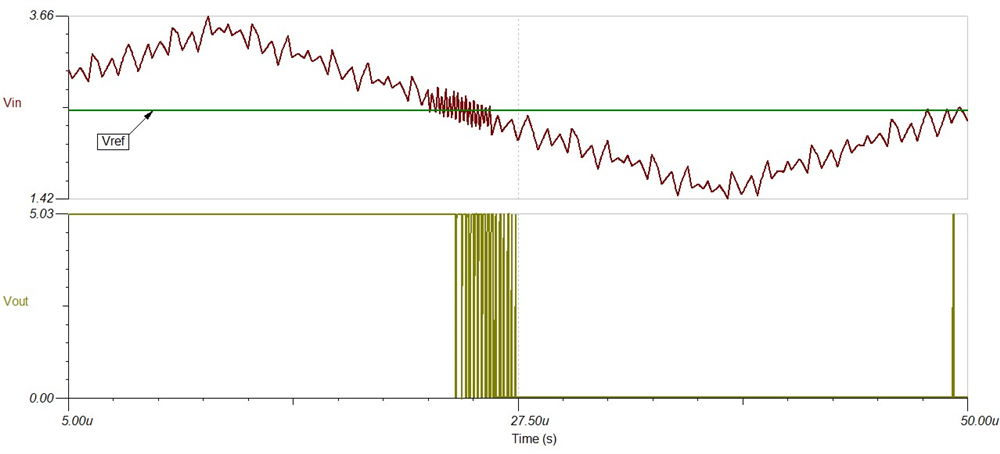

圖 7 和圖 8 顯示採用了遲滯、濾波和適當旁路以及電路配置後的結果波形。使用「採遲滯電路的非反相比較器」中的公式,選擇值 R1 = 100 kΩ、R5 = 10 kΩ、VHYST = 500 mV、VO(max) = 5 V、VO(min) = 110 mV 和 VREF = 2.5,R2 的計算值 = 100 kΩ、R3 = 49.9 kΩ 和 R4 = 442 kΩ。請注意,所有電阻值都四捨五入到最接近的 1% 標準電阻值。

圖 7:比較器的顫振獲得解決

圖8:外部遲滯及濾波的非反相比較器設定

總結

為了加強對抗雜訊(以及隨之而來的顫振),某些時序和準度規範可能無法達成。進行濾波或遲滯可以提高系統效能,但我建議同時雙管齊下,才能最大程度地減少顫振。請記得,執行遲滯會改變閾值電壓,做選擇時要反映系統要求。還要注意濾波如何影響系統的時序限制。

建立抗雜訊能力對所有系統來說都相當重要,能最大限度地減少比較器故障和不需要的效能。本系列文章的的第二篇,我們將討論輸入的共模電壓範圍。