Part Number: J784S4XEVM

By default, the second PCIe slot is not configured for PCIe root complex mode from the SoC-side, meaning if we wanted to connect an end point device like a NVMe SSD card, the link does not go up.

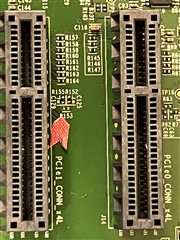

When connecting a NVMe SSD card to the second PCIe slot J17 which is connected to 2 lanes of PCIe, boot logs reports "Failed to init phy". Link for PCIe is only initialized on the first PCIe slot in J14, which is connected to 4 lanes of PCIe.