Part Number: TDA4VH-Q1

Other Parts Discussed in Thread: TDA4VM, TCA9539

My SDK version:

linux: ti-processor-sdk-linux-adas-j784s4-evm-09_01_00_06

rtos: ti-processor-sdk-rtos-j784s4-evm-09_01_00_06

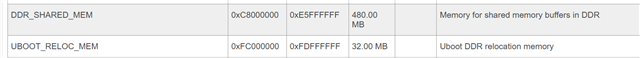

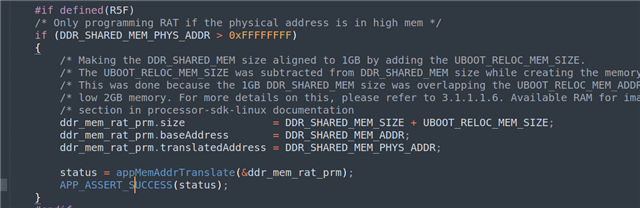

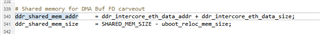

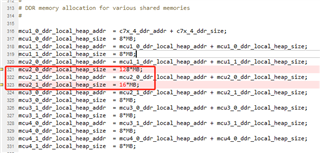

I tried to change the heap memory size of MCU2_0, after referring to the instruction manual, I changed the "

Rtos_sdk vision_apps/platform/j784s4 / rtos/gen_linker_mem_map.py " files, and execute the script, obtained the corresponding generated file. The changes are as follows:

Copy the contents of the k3-j784s4-rtos-memory-map.dtsi file to the appropriate path of the Linux SDK and compile and install it according to the instructions in the instruction manual.

1. To generate the memory map related files do below

cd vision_apps/platform/<soc>/rtos

python3 gen_linker_mem_map.py

2. Copy the contents of the generated k3-{SOC}-rtos-memory-map.dtsi file and replace the reserved_memory section of the k3-{SOC}-rtos-memory-map.dtsi file that is located here:

PSDK_LINUX_PATH/board-support/linux*/arch/arm64/boot/dts/ti

3.1 Rebuild the dtb and dtbo from the PSDK_LINUX_PATH directory with the following:

make linux-dtbs

3.2 Install the dtb and dtbo to the rootfs/boot folder on the SD card from the same directory with the following

sudo make linux-dtbs_install; sync

After compiling and installing both the RTOS and Linux into the SD card, boot the system:

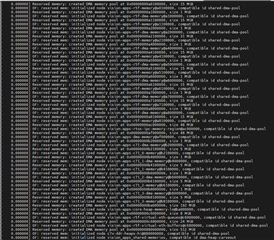

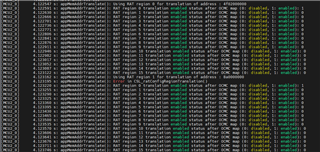

From the memory size and memory address, you can see that I have configured it successfully.

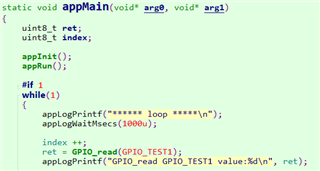

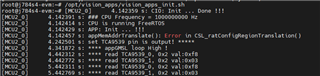

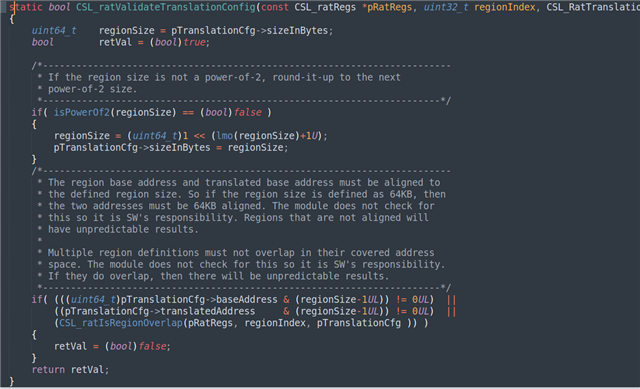

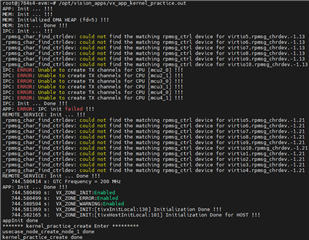

Running my test program produces the following error:

What is the cause of this problem? How to fix it?

Above, thank you