本稿では、インターフェイス・トポロジが逐次比較型(SAR)アナログ/デジタル・コンバータ(ADC)のスループットと応答時間に与える影響について検討します。

SAR ADCは一般的にアクイジションと変換の2つの動作フェーズで構成されており、次のように機能します。

- アクイジション・フェーズでは、サンプル・ホールド・スイッチが閉じており、SAR ADCは外部アナログ入力をサンプリング・コンデンサに取り込みます。その後、ホスト・コントローラが変換開始(SOC)信号を発して、アクイジション・フェーズを終了させ、アナログ/デジタル変換の処理を開始します。

- 変換フェーズでは、SAR ADCはサンプリングした、つまり取り込んだアナログ入力を、二分探索アルゴリズムを用いて等価のデジタル・コードに変換します。デジタル・データ出力はADCとホスト・コントローラの間でデジタル・インターフェイスを使用し、ホスト・コントローラに伝送されます。

各用語の定義は次の通りです。

- tTHROUGHPUT:2つのSOC信号間などの、連続する2つのサンプル間で維持されるべき最小時間差

- tCONV(変換時間):サンプリングしたアナログ電圧をADCが等価のデジタル・コードに変換するために要する時間

- tACQ(アクイジション時間):ADCがアナログ入力信号の取りこみに要する時間

- tDTX(データ伝送時間):ADCが変換結果をホスト・コントローラに伝送するために要する時間

- tRESP-ADC(応答時間):ホスト・コントローラがSOC信号を発してから変換結果を受け取るまでの時間差

- tRESP-ADC-m(m-bitに対する応答時間):ホスト・コントローラがSOC信号を発してからmビットの変換結果を受け取るまでの時間差

tCONV、tACQ、スループットの仕様は、SAR ADCのデータシートに必ず明記されています。しかし、データ伝送時間(TDTX)の検出は、特に複雑でフレキシブルなインターフェイスを有するデバイスの場合、かなり注意を要することがあります。

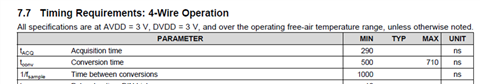

以下に示すのは、一般的なSAR ADCのタイミング仕様です。

変換結果をホスト・コントローラに返送する際のさまざまな方式と、これらのインターフェイス・トポロジがtTHROUGHPUT とtRESP-ADCに及ぼす影響について解説します。

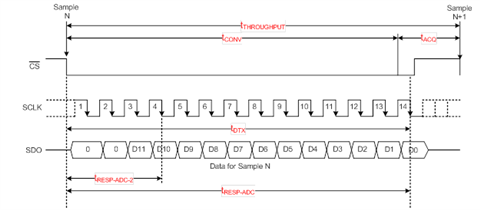

インターフェイス・タイプ1:データ・ビットを分解し、伝送

これが最も簡単なインターフェイス方式です。この方式のSAR ADCは一般的に外部クロックで動作します。ADCはクロックごとに1つの追加ビットを分解し、分解ビットは(ほぼ)即座に同じクロックを使用してホスト・コントローラに伝送されます。図2はTIのADS 7042に実装されているこのタイプのインターフェイスを示します。

例えば、ADS 7042のスループットは1Msps(tTHROUGHPUT = 1µs)ですが、応答時間はそれより速い844nsです。

- tTHROUGHPUT = tCONV + tACQ

- tDTX < tTHROUGHPUT

- tRESP-ADC = tDTX

- tRESP-ADC < tTHROUGHPUT

さらに、外部クロックのクロック周期がtCLKで、ADCの分解能がnの場合、個々のtCLKの時間間隔でホスト・コントローラは新しい1ビットの情報を入手できるようになります(ただしクロック周期2つ分、2 tCLKの初期遅延を伴います)。従って、次のように定義できます。

- tRESP-ADC-1 = 3 * tCLK

- tRESP-ADC-2 = 4 * tCLK

- または一般的にtRESP-ADC-m = (m+2) * tCLK(ここでm < n)

このタイプのインターフェイスが有効な例

例えば、ADS 7042を使用する制御システムで次の要件が求められる場合:

- 0~3*VREF/4の範囲の入力信号を12ビット精度で分解

- 3*VREF/4を超える入力信号には速やかにアラーム・フラグを立てる

入力信号がアラーム範囲になった時、ADS 7042から出力される最初の2ビットは「11」になります。図2に示すように、ホスト・コントローラはこの情報を時間tRESP-ADC-2で入手できるので、直ちに(変換処理の完了を待たずに)アラームを発することが可能です。

入力信号が正常範囲の時(つまりADS 7042の出力の最初の2ビットが「11」でない時)、ホスト・コントローラはより多くのクロックを提供し、残りのすべてのビットを分解し、最終的に12ビット精度の出力コードを得ます。

このタイプのインターフェイスの制約について

ビット値決定に何らかのエラーが生じれば、直ちにホスト・コントローラに送信されるため、間違った制御動作を招くことがあります。

こうしたビット値決定エラーが起きる確率は、スループットが高いほど、また高分解能であるほど上昇します。従って、通常、このタイプのインターフェイスは低分解能または低速のADCに限定されます。

このシリーズの次稿では、より高精度(12ビット超)で、特にスループットがより高い(100Ksps超)のADCに使用される他の2つのタイプのインターフェイスについて検討します。

その他のリソース:

- SPIインターフェイスを備えた超低消費電力、超小型12ビット1Msps SAR ADCのTIのADS 7042のデータシート、無償サンプル

- 低消費電力で超小型サイズ設計に最適な3つの12ビット・データ・アクイジション・リファレンス・デザイン(TIPD 168)

- SAR ADC response timesシリーズの他のブログ(英語)

上記の記事は下記 URL より翻訳転載されました。

*ご質問は E2E 日本語コミュニティにお願い致します。