The analysis you have provided does not seem to line up with the results from physical testing.

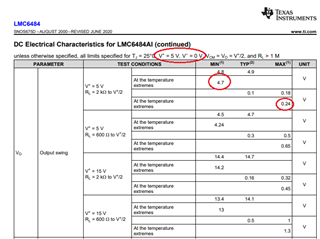

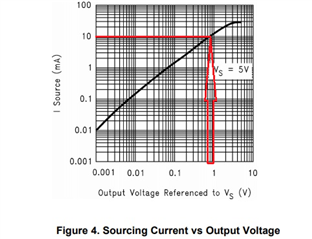

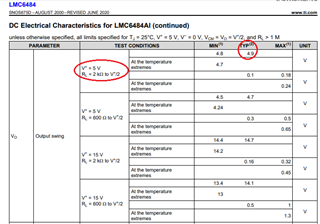

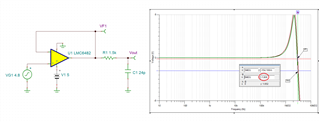

From your simulations, the LMC6474, the rise time of the output is ~5us however, given that MAX1230 ADC acquisition time is <0.6us, this would result in ADC output being nowhere near 5V - we are seeing around 4.7V when 5V is applied.

I have simulated the sample-hold function with 0.6us pulse applied to the switch to represent the acquisition and the Vout reaches 5V well within this time.

I still dont know why we are seeing a drop in ADC output i.e. when we apply 4.9V DC to the input the output is around 4.7V...

(both simulations produce the same results)