Other Parts Discussed in Thread: TINA-TI

Hi Team,

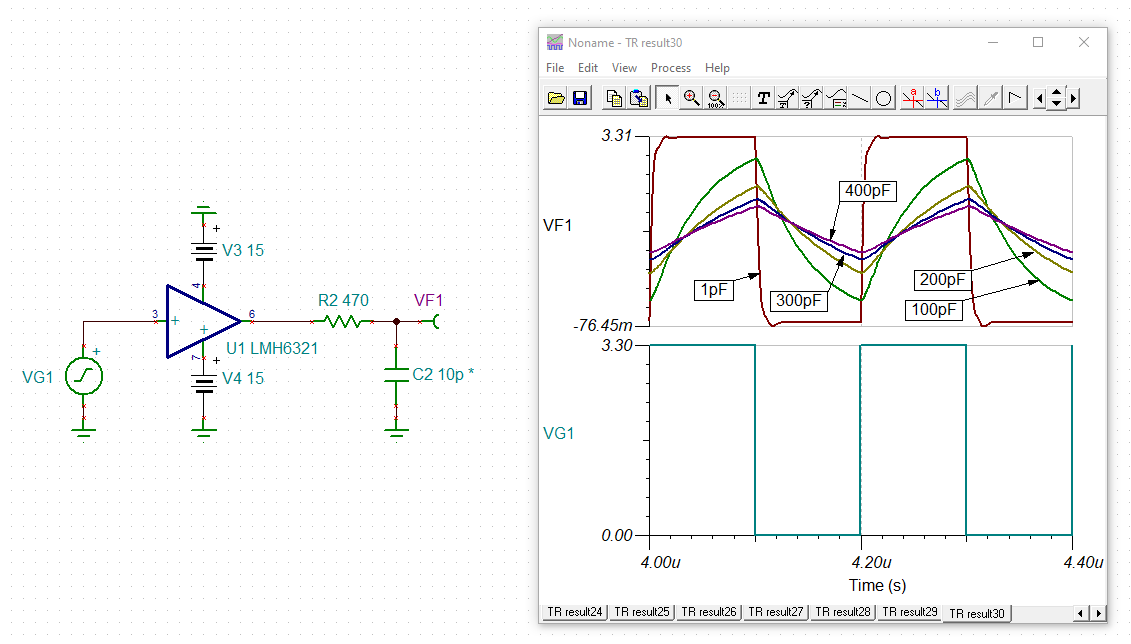

Good day. I have a high-speed signal coming to a PCB and I wasn't able to use the high-speed signal (about 20Mhz) directly to the digital input-output card, because of high parsatics capacitance (about 400pf probably). So now that I use LMH6321 as a buffer to improve the slew rate. Please find the schematic for the same.

I see some delay than expected in the real PCB.

I left the CL open. ( would it cause a problem?)

also attached are some scope signals for 5Mhz as input and 20Mhz as input.

green signal- output from the buffer LMH6321 and Red signal- input to the buffer.

So my questions:

1) I see that if we use some polarised high capacitors as supply bias pass capacitors, would it help to improve slew rate?

2) And is there some better circuit to use it as a buffer for high frequency(20Mhz) and high capacitive load(400p).

P.S I could also control my input at DIO to HIgh impedance or 50 ohms, if then what circuit can be best used?

Best Regards,

Tarun Kumar

---> When i use High Impedance termination at the input of the digital card.

---> When i use High Impedance termination at the input of the digital card. -->when i used 50ohm termination at the input of the digital card.

-->when i used 50ohm termination at the input of the digital card.

--> after changing to copper wiring at a clock speed 20Mhz

--> after changing to copper wiring at a clock speed 20Mhz --->befor coper wire at a clock speed of 17Mhz

--->befor coper wire at a clock speed of 17Mhz -->15Mhz

-->15Mhz --> 16.6Mhz

--> 16.6Mhz --> 17Mhx

--> 17Mhx -->18Mhz

-->18Mhz --20Mhz

--20Mhz

--> 20Mhz clock frequency

--> 20Mhz clock frequency ---> 20Mhz input frequency.

---> 20Mhz input frequency.