Other Parts Discussed in Thread: LM3489, LP5907

Hello

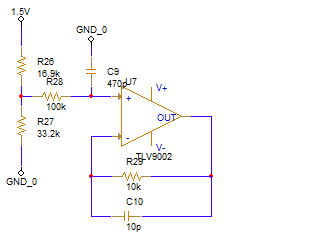

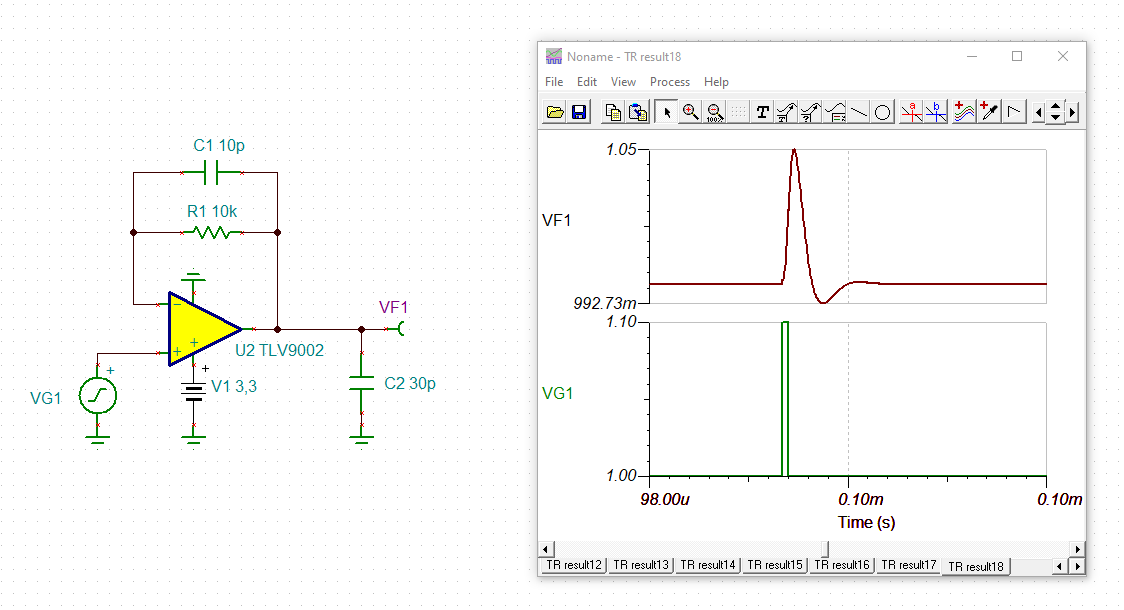

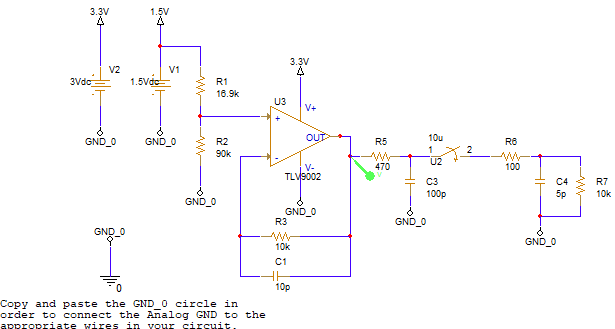

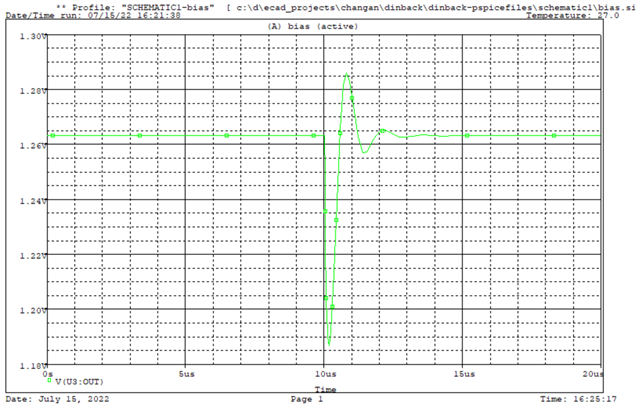

I observe a strange output of TLV9004. In the following schematic, the output of the amplifier should be roughly 1V, a DC value.

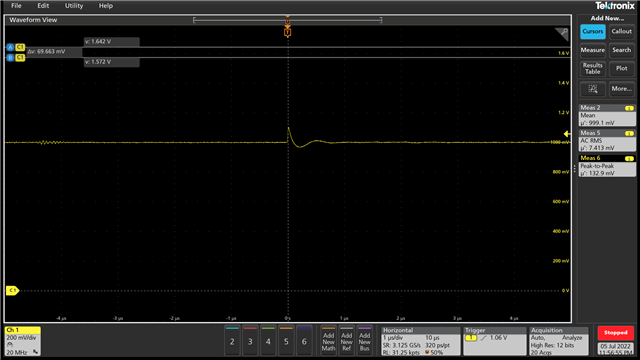

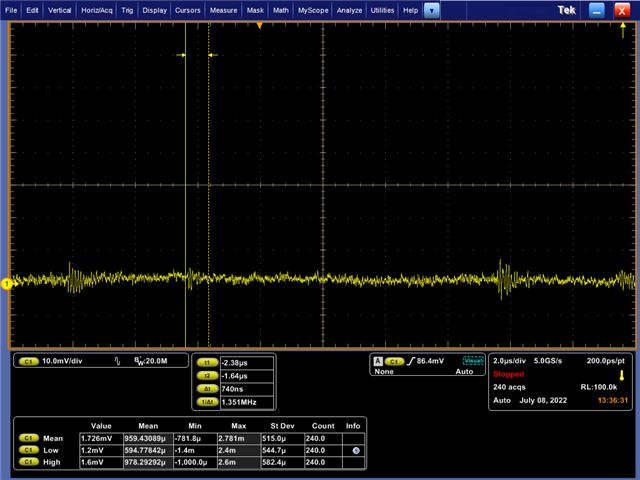

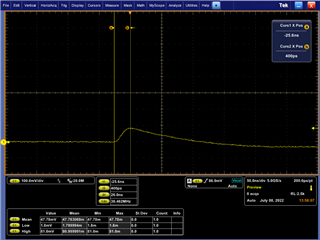

But I see a strange oscillation in the output. The output of the amplifier is connected to 1G3157 as one of the input. But when I remove the switch, the problem still exist.

The non-invert input of the amplifier seems quite normal. But the invert input of the amplifier seem quite strange with the glitch.

Thanks for supporting