Hi team,

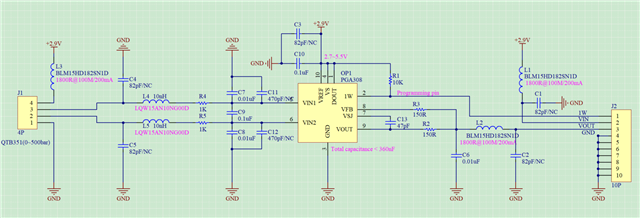

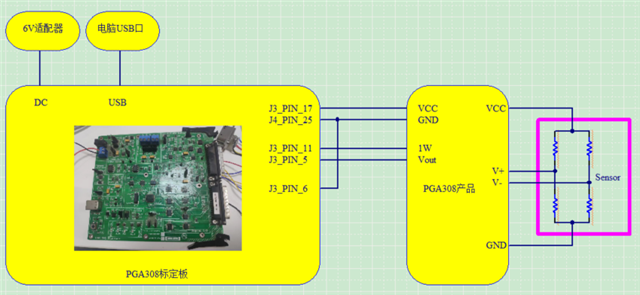

One of my customers is evaluating PGA308 on their own board.

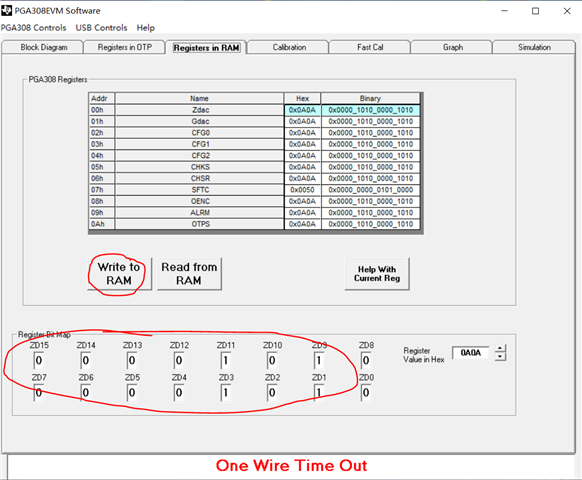

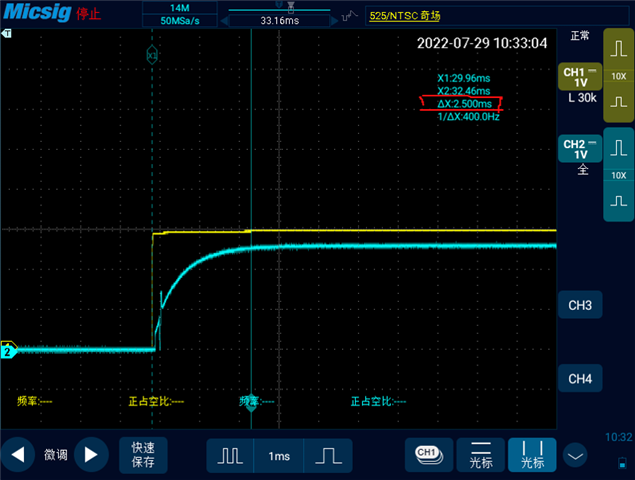

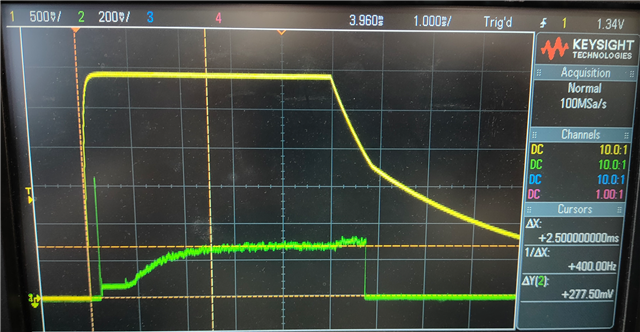

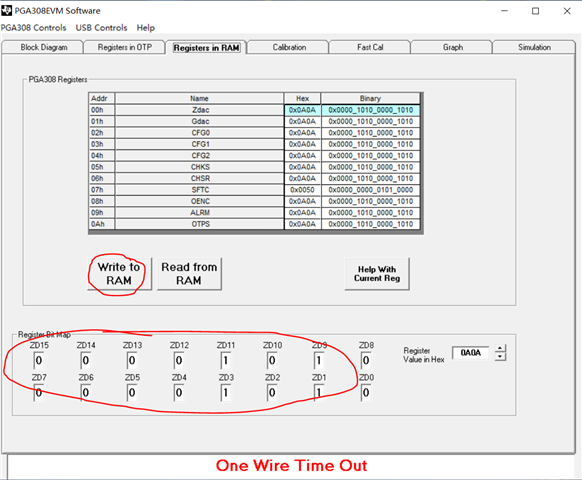

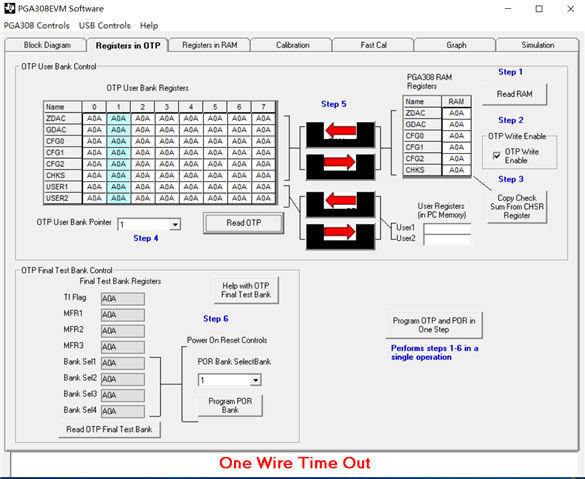

My customer changed CFG2 to 0XDC0 by first modifying the register in the Register bit, after clicking Write to RAM. But my customer doesn't know if that's correct, and what the next steps are? Could you help me to solve this problem? You reply would be much appreciated.