Other Parts Discussed in Thread: LM4040, MUX36D08, , ADS8318, OPA4192

Unexplained noise showing up in multichannel temp data acquisition system. Advice sought.

Background:

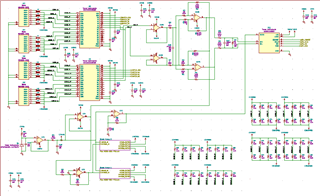

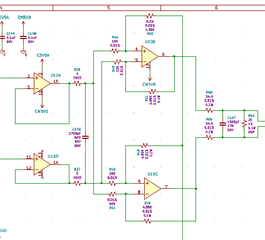

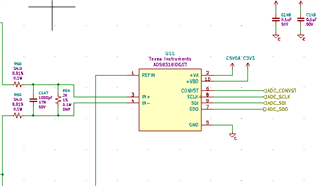

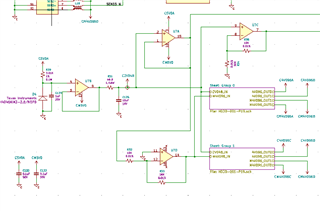

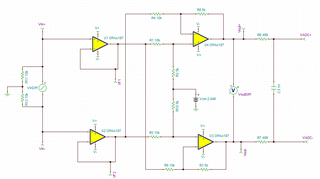

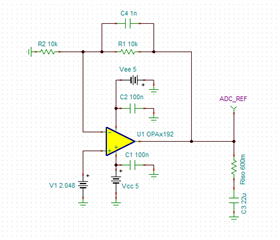

All bridge, ADC reference voltages generated from amplified 0.1% tolerance TI LM4040 2.048V precision reference. Bridge reference voltages +/- 4.096V. ADCreference 4.096V. Cross couple diff amp pair common mode reference voltage = 2.048V.

Fully balanced circuit using bridges with ntc thermistors as the sensors.

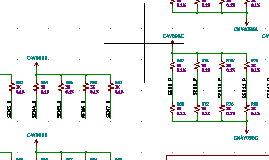

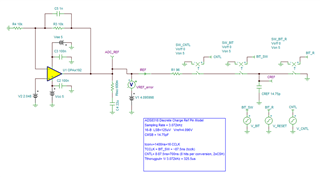

16X sensors signals multiplexed via 2X TI MUX36D08 multiplexers.

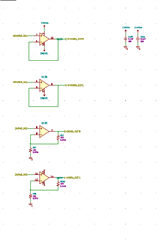

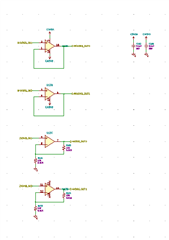

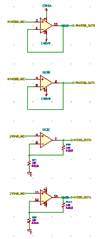

The mux 's are followed by OPA4187 opamps in instrumentation amp configuration and utilizing a pair of cross coupled differential amps (all 0.01% resistors), gain of 0.5. The positive and negative outputs have common mode voltage of 2.048V and can swing between 0-4.096V.

ADC's input antialiasing filter consists of a balanced differential filter. There is series 24.9 ohm resistors and a 1nF COG cap in parallel with 2k ohm.

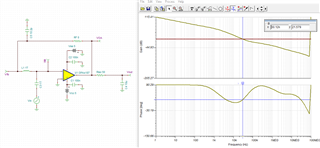

Sample rate well under 1MHz...around 500kS/s if I recall correctly.

Precision reference, MUX's, opamps, ADC's all running from clean linear regulated +/- 5V rails.

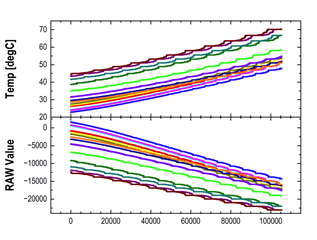

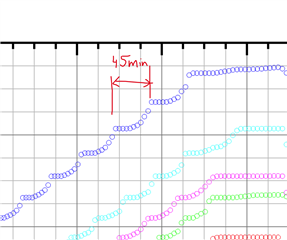

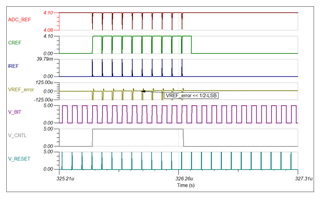

Attached is a screenshot of the temp data taken by our product using this data acquisition circuit described above. Notice the scalloping in the data at higher temperatures and the very long time scale the occur within. I am at a loss to explain why this is happenning.

Could this be some artifact of the temp compensation choppers/servos in the opamps?

What in the world is going on here?