Other Parts Discussed in Thread: TLV1701, , TINA-TI

Hi,

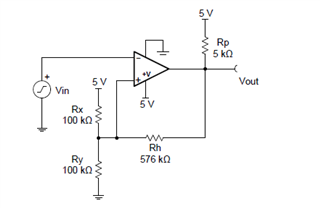

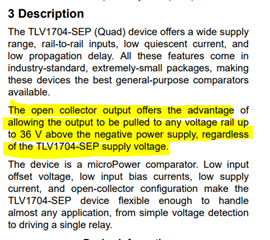

When using the default TINA-TI model provided for the TLV1704-SEP (which is the TLV1701 spice model) I noticed the following behavior.

As shown below, when using the default model TLV1701 (spice model date : 12/16/2013) , we can see that the output (COMP_OUT) remains LOW during Supply ramp up.

However, when using the newest spice model from 08/30/2023, we can see that the output goes High and then LOW during supply ramp-up.

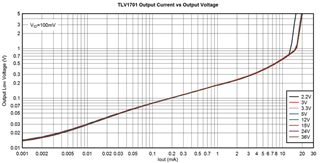

Looking at the image below (COMP_OUT in red) we can see that the comparator drives the output LOW when VCC is about 2.17V.

I also run this simulation using another Spice Simulator and got the same results.

My assumption is that the newer Spice model reflect the expected behavior of the comparator meaning that the comparator is not able to drive the output until VCC reaches 2V.

1. During power ramp up, what is the expected state of the output when VCC < VCC MIN (2.2V).

2. Should we expect the OUTPUT to follow VCC due to the external Pull-up at the output or is the output should be LOW ?

The circuit that I'm using is the same as the one below except that VCC = 3.3V and I used different resistor values to obtain a different Threshold.