Other Parts Discussed in Thread: LMP7717, TINA-TI

Dear Engineers,

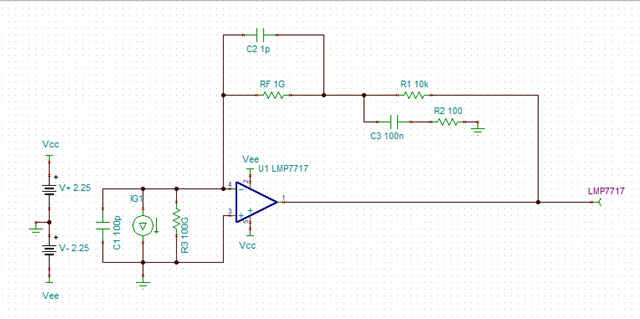

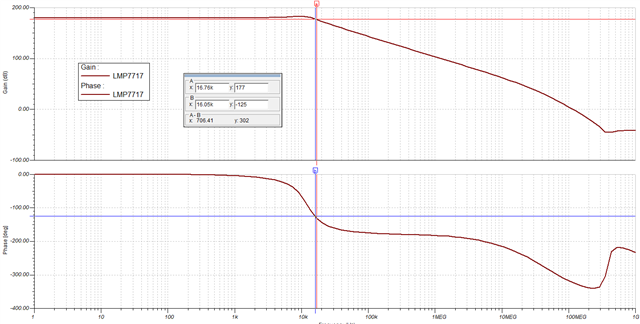

We want to design a transimpedance amplifier with a gain over 1G V/A, and we also want its bandwidth to be as high as possible. We already know the impact of input capacitance and feedback capacitance on the circuit, and the parasitic capacitance of high-resistance feedback resistor will play the same role as the feedback capacitance. Therefore, we learned the design methods of some papers and improved the feedback loop.

We found that the TINA-TI simulation results of the improved circuit show that the OPA818 should perform better than the LMP7717, but in actual testing the LMP7717 can achieve higher bandwidth(about 20KHz).

Our question is:

1.How to explain the contradiction between simulation and physical experiments?

2.Is the parasitic capacitance of the 1G ohm feedback resistor 1pF? (Because it is difficult to measure the actual circuit, we have to estimate it)

3. Is OPA818 the best chip we should choose?

These are our file:

/cfs-file/__key/communityserver-discussions-components-files/14/4812.opa818.TSC

/cfs-file/__key/communityserver-discussions-components-files/14/2364.lmp7717.TSC

Thanks for your help