Hi,

I'm using the OPA564 with Vanalog = +/-5,5V.

I read in the datasheet that (V–) + 3.0V ≤ VDIG ≤ (V–) + 5.5V

So I understand that I my Vdig must be comprised between -2.5V and 0V, so it must be negative.

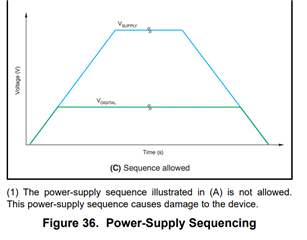

But I can not understand how to realize the power-on sequence described in the fig.36 of the datasheet. Does that mean that I have to start my Vdig sequence from -5V5?

Moreover, does Vdig negative means that all the flags will be negative too?

Thanks,

Sylvain