Other Parts Discussed in Thread: TLV1811, TLV1805,

Hello,

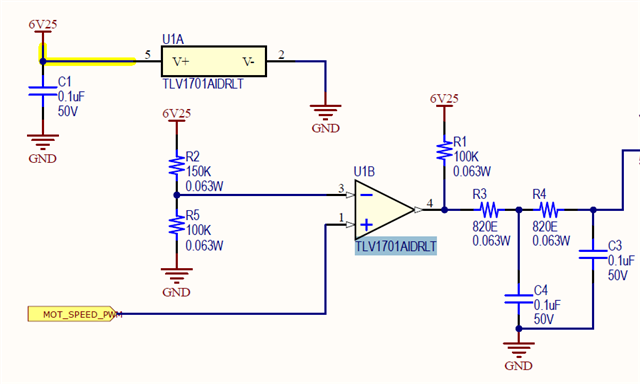

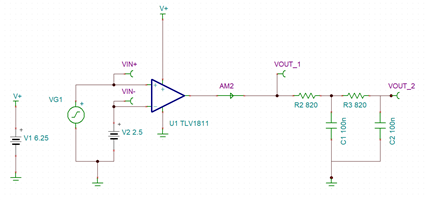

Please find our below circuitry ,

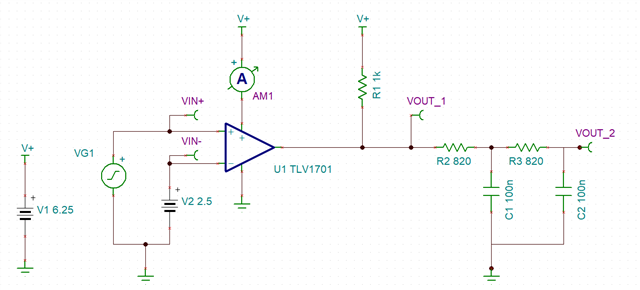

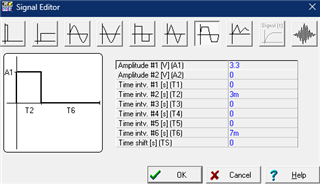

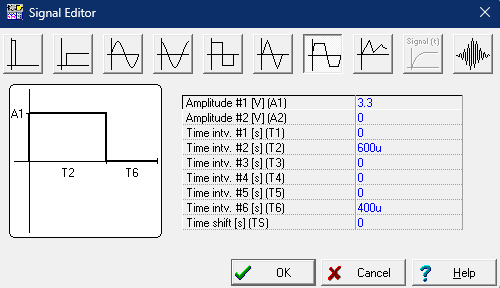

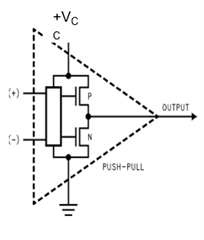

MOT_SPEED_PWM is a 3.3V PWM Signal , we are using opamp for level shifting it to 6.25V keeping 2.5V at reference.

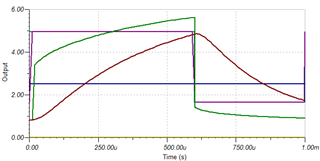

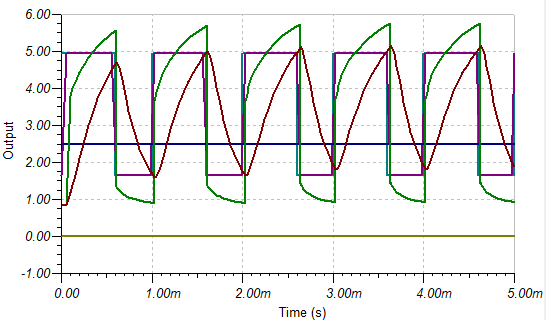

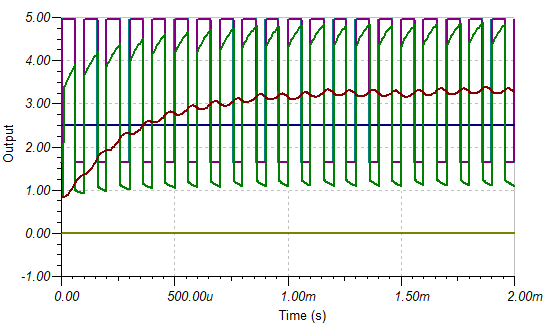

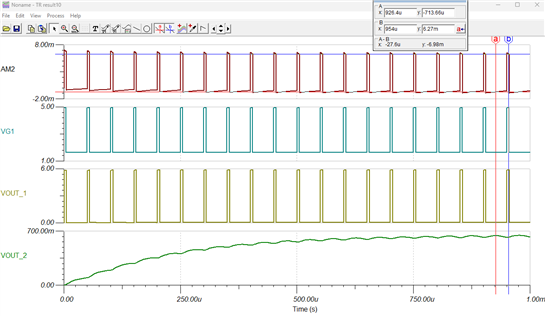

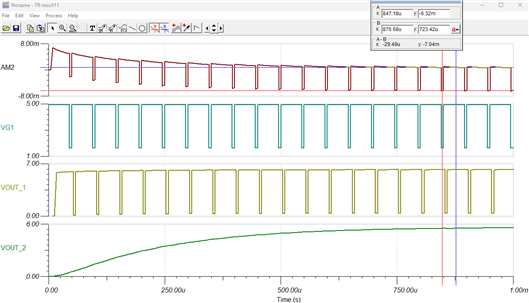

The 6.25 PWM output is later required to convert into DC. So second order RC Filter is used.

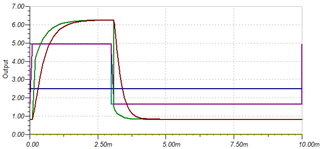

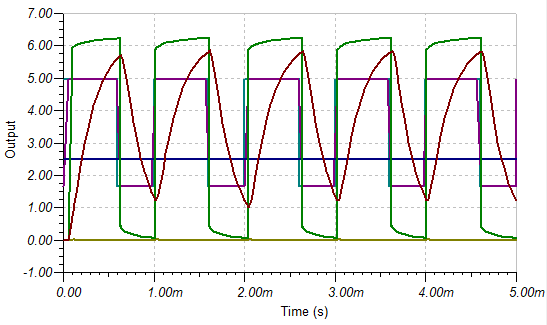

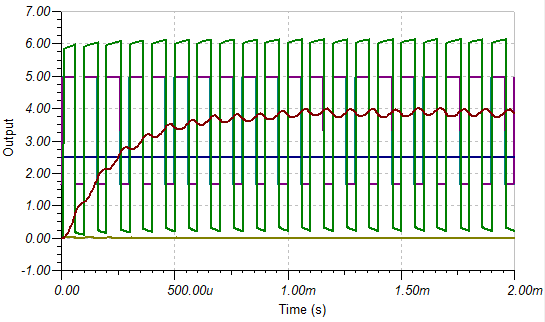

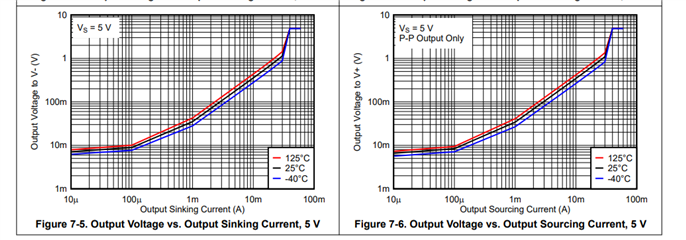

But because of this i am not able to see 6.25V at the output , it is getting dipped down.

As I increase the TON of MOT_SPEED_PWM Signal, Output is getting increased gradually , But this is impacting the rest of the circuitry. Is there are any suggestion for this?