Hello team,

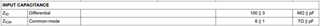

There are specs about the input impedance.

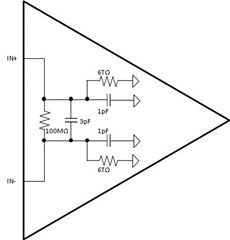

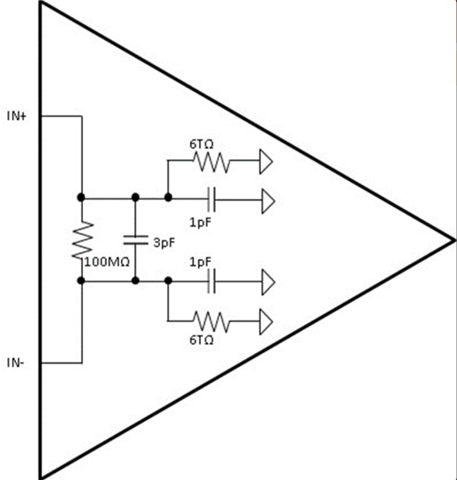

Does this mean below? (Capacitance and Resistance are in parallel?)

Regards,

Hirata

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello team,

There are specs about the input impedance.

Does this mean below? (Capacitance and Resistance are in parallel?)

Regards,

Hirata

Hirata-san,

Yes.

Best,

Jerry

Jerry-san,

Thanks for your answer. I understood.

Let me ask one more question.

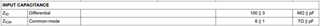

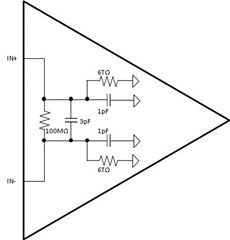

The modeling of the input impedance of this TLV9352 PSPICE model is exactly same as this resistor/capacitor network specified in datasheet(below)?

It looks very similar(almost same) but looks not exactly same so would like to know.

Regards,

Hirata

Hey Hirata-san,

Differential impedance should be correctly modeled as the parallel resistor and capacitor with the correct values.

I'm fairly certain that the 6TOhm resistors are probably just 1T resistors, which are the standard placeholders. It might not make a difference in simulation as there is a minimum current specified in the simulator. Increasing a resistance from 1TOhm to 6TOhm will not make a difference.

Best,

Jerry

Hi Jerry-san,

Thanks for your insight. I understood.

I appreciate your support, as always.

Regards,

Hirata