Tool/software:

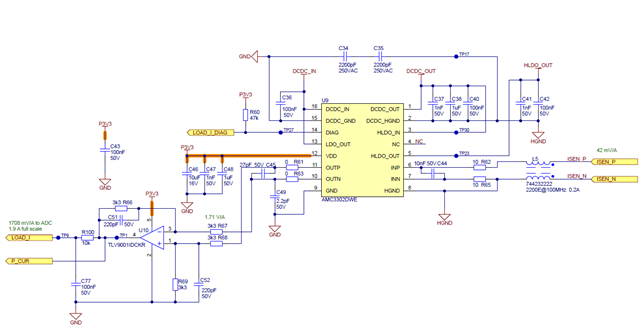

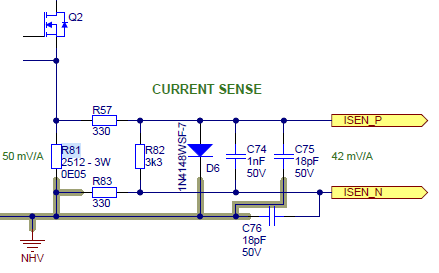

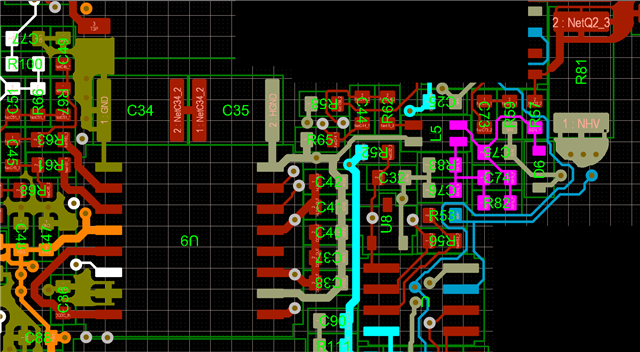

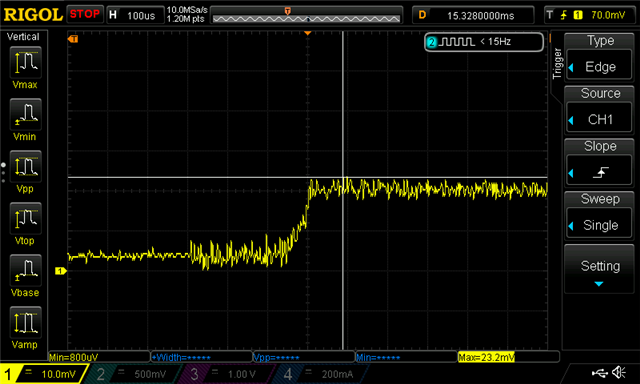

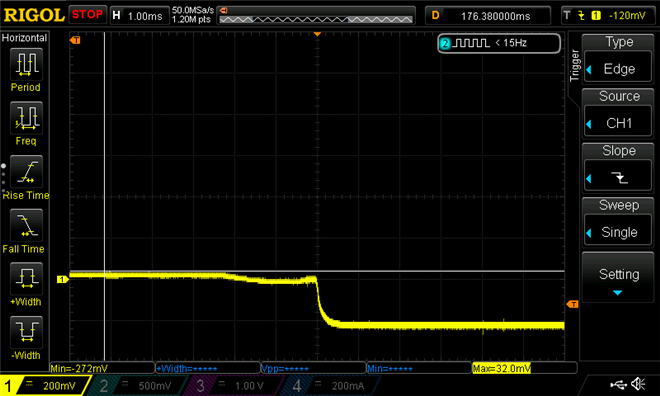

Hello, I have observed a DC bias offset at AMC3302 IC input in our design used for current sensing.

The +17mVDC offset is quite large with respect to the maximum full scale linear differential input voltage of ±50mV and way more than the datasheet specified ±50µV.

The design incorporates multiple galvanic isolators for 4 isolated nets by means of transformers, optocouplers and the iso-opamp AMC3302, effectively isolating SELV and LIVE parts.

The offset becomes present when +24VDC is supplied on the SELV side, without connecting any loads or enabling any isolated nets.

Basically, only +3.3VDC is supplied to VDD.

Do you have any advice or idea please?

Thank you in advance and best regards,

Fabien