Other Parts Discussed in Thread: ADS1250, LMP7701

I'm testing a new board that is an AFE for conditioning the signal coming from a photodiode;

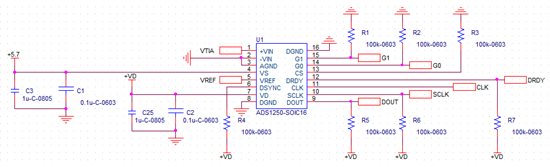

in this project I'm using the ADS1250 to digitize the analog signal;

the power supply architecture is following described:

there is a master power line coming from a switching regulator that give 12V;

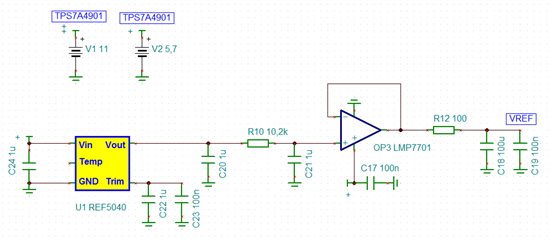

the input of a TPS7A4901 is connected to the master 12V and the output of this ldo is 11V; the output of the TPS7A4901 that give 11V is connected to the input of another TPS4901 to reach 5.7V;

+VD is given by a MC78L05ACD with the input connected to the master 12V;

to give the reference to the ADS1250, I'm using the following circuit:

all the capacitor is MLCC, the 100uF on the LMP7701's output is tantalum capacitor;

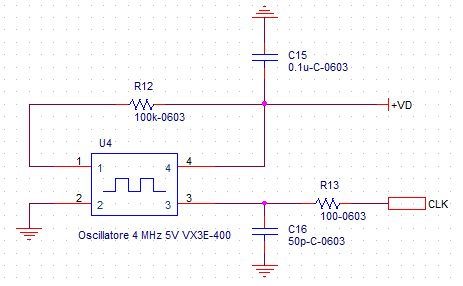

the ADC's clock frequency is 4 MHz;

ADC, clock, reference and power supply is on the same board and an heavy ground plane is used to distribute the ground in the board;

AGND and DGN of the ADS1250 is connected together with a wide copper area in the top layer and this copper area is conected to the ground plane with a via hole

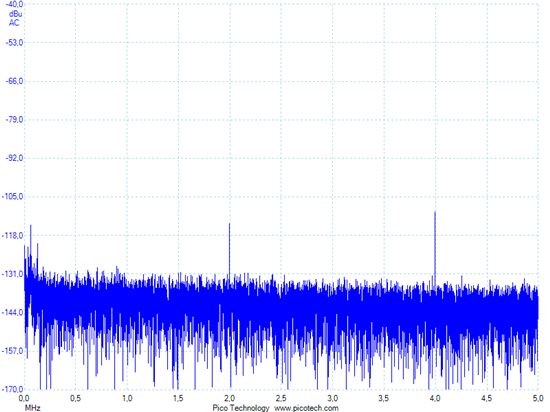

if I measure the FFT of VREF on C19 with the clock signal disconnected to the ADS1250 I obtain the following graph:

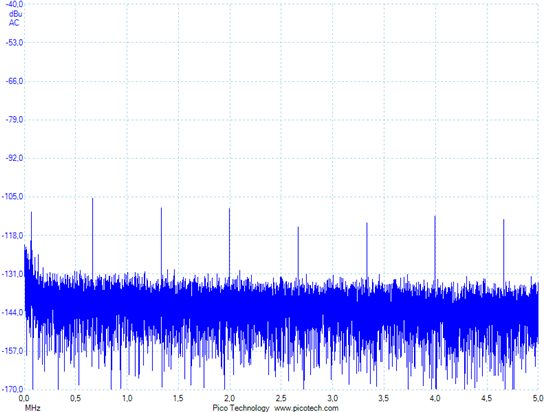

if I measure the FFT of VREF on C19 with the clock signal connected to the ADS1250 I obtain the following graph:

As can be seen from the graphs, a lot of different harmonic components appear when I connect the clock signal to the ADC;

have someone ever seen this behavior before?

I would like to kill this spurious signal because I have to reach the lowest noise level possible;

someone have the solution?

thank you in advance for the answers;

if I have forget something, please, don't exitate to ask me;

Fabrizio