hi dear supporting team,

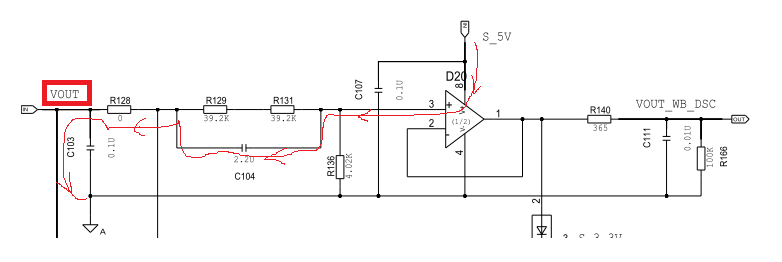

my customer is using OPA2354 in their power module, circuit as below:

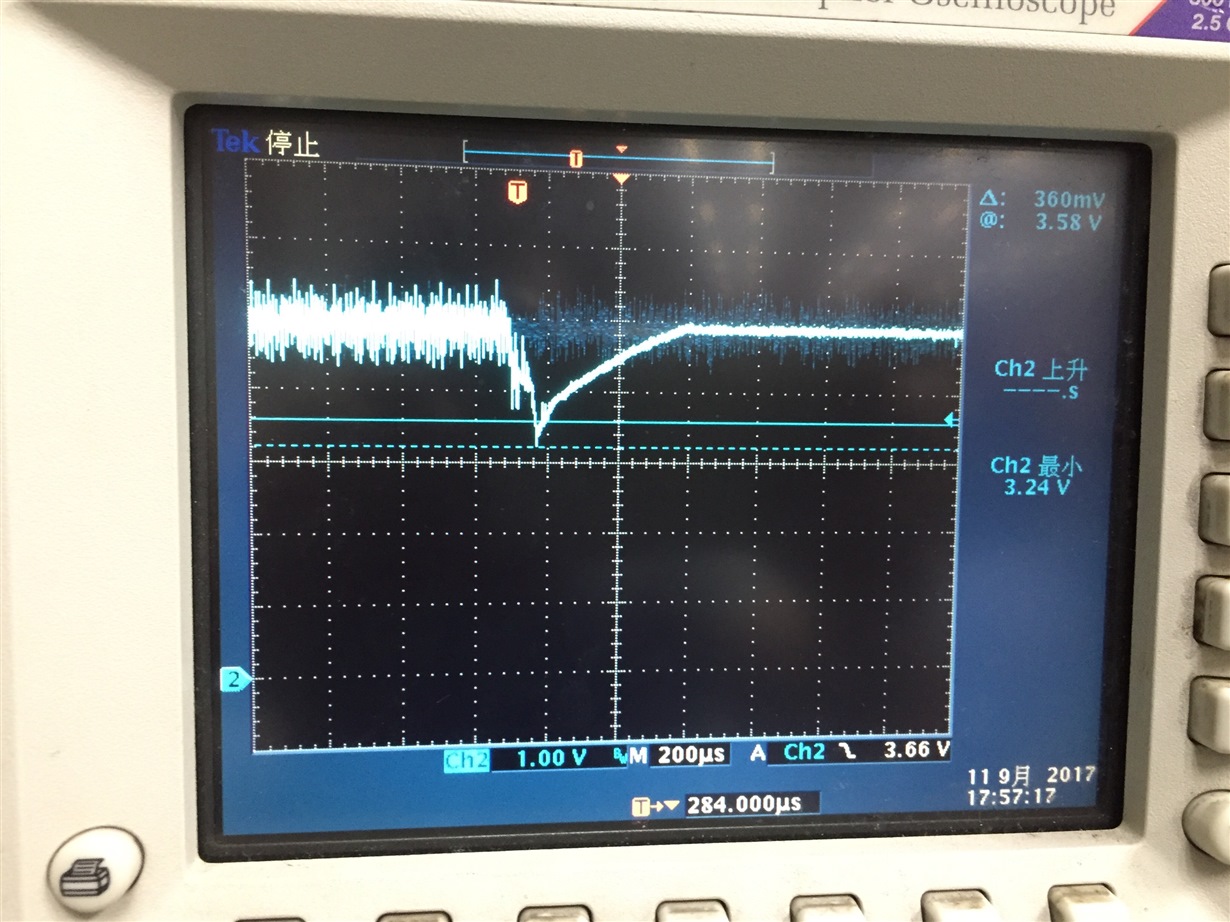

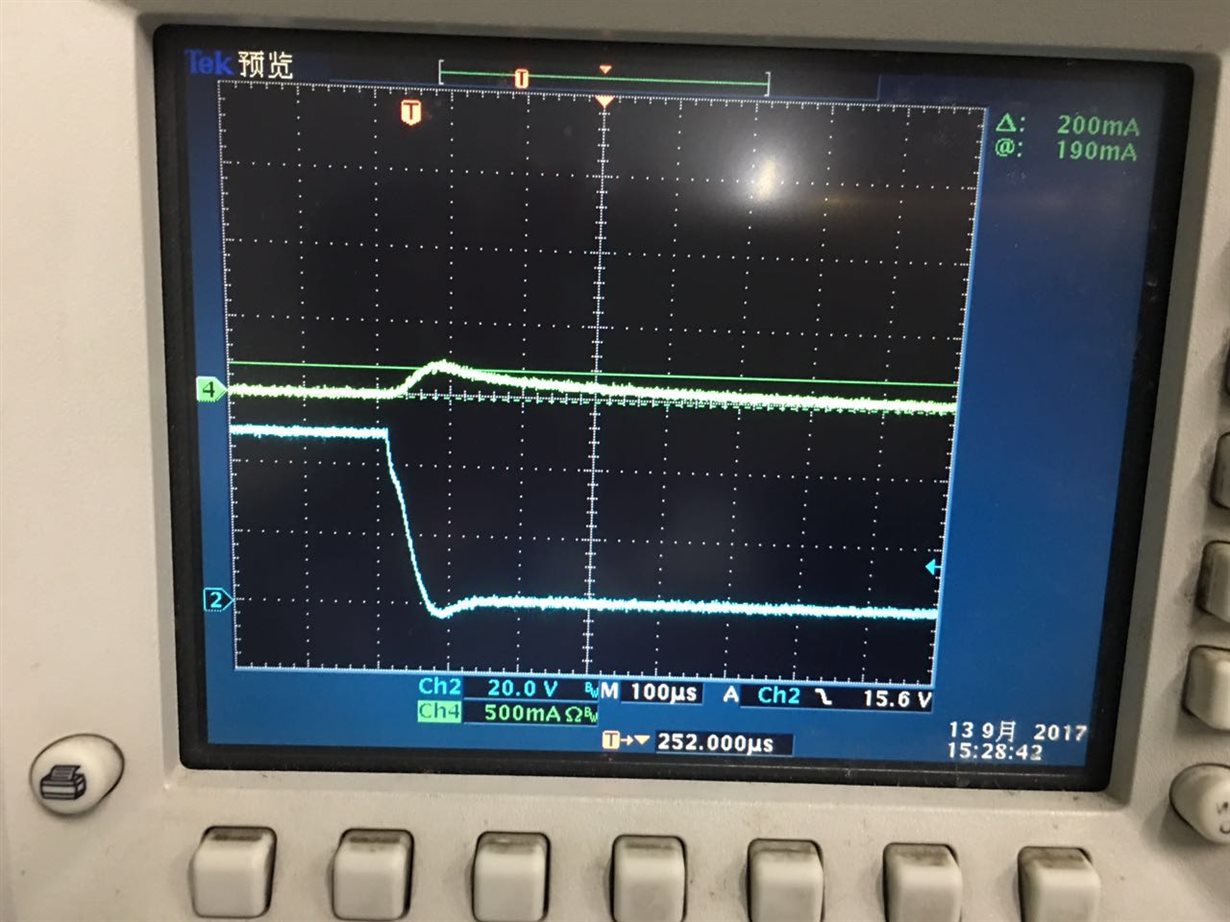

they need do short circuit experiment which will short the Vout poin in red circle below to GND for 1~2hours. when they short the point, they will find the power supply for OPA2354 will drop to ~1.5V, as below:

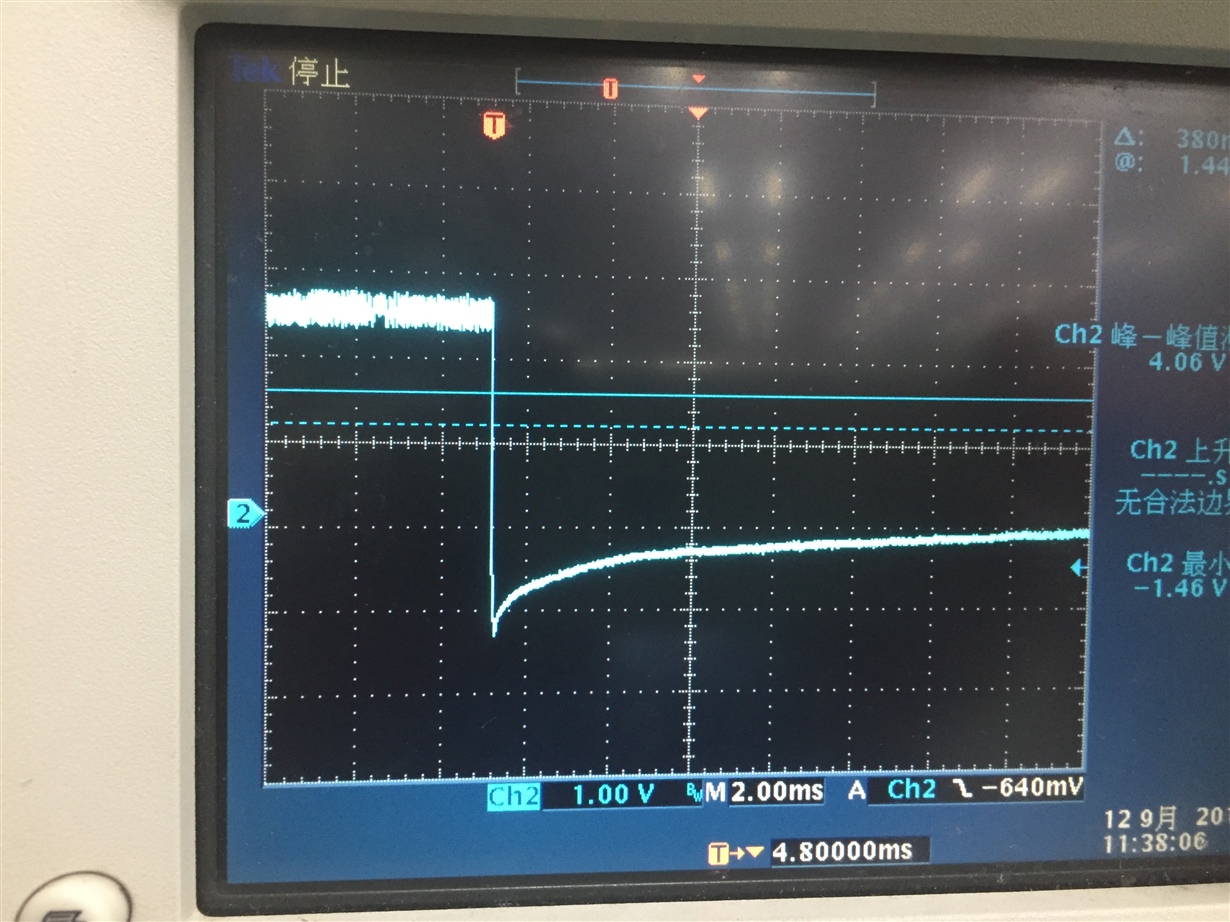

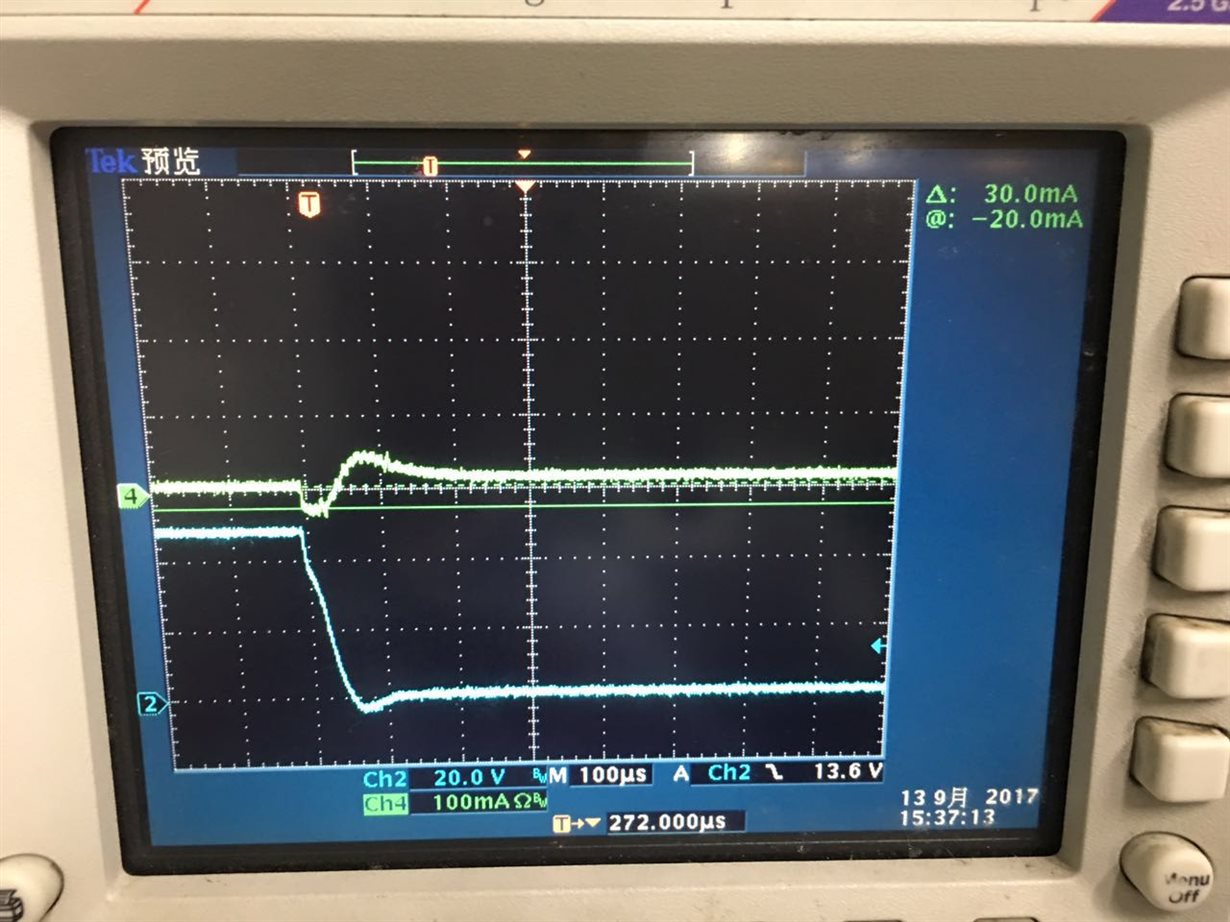

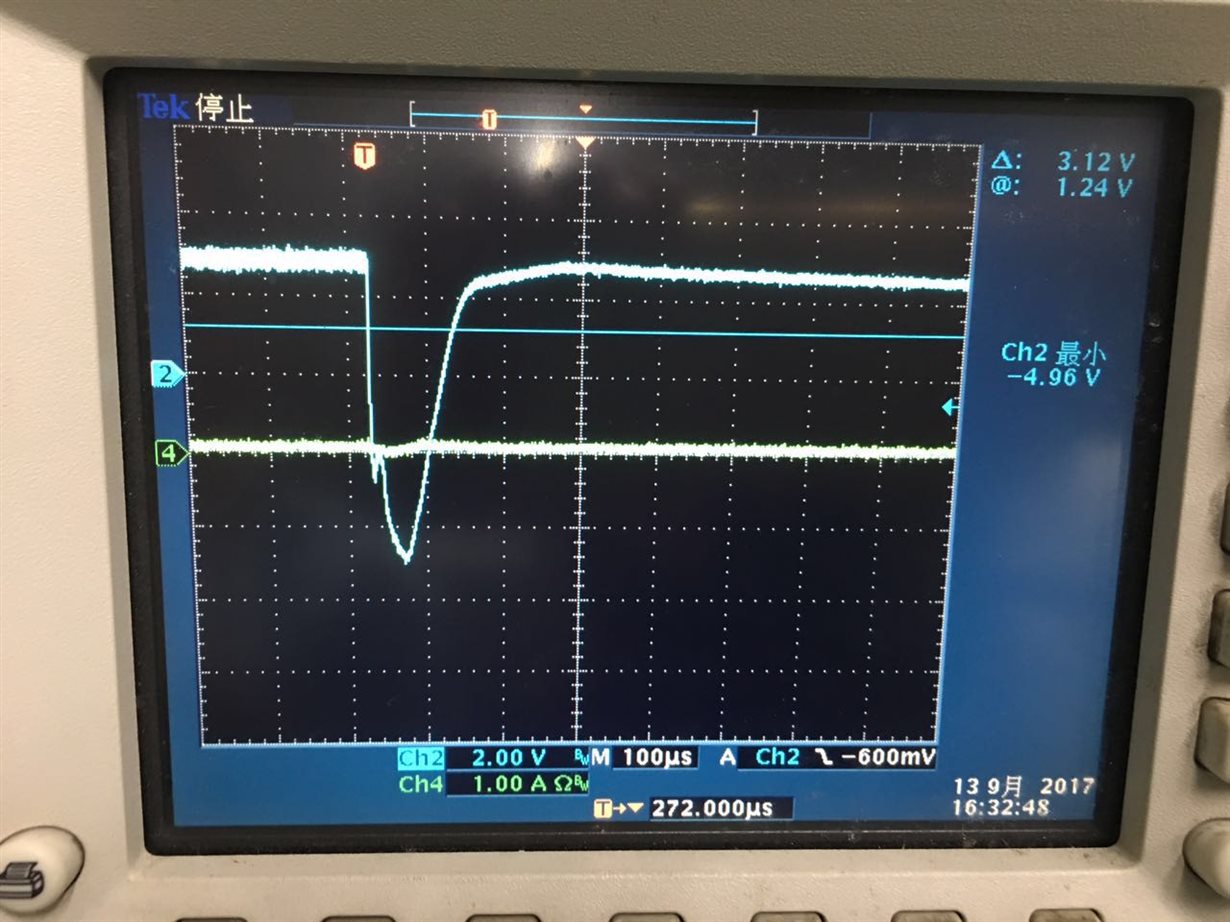

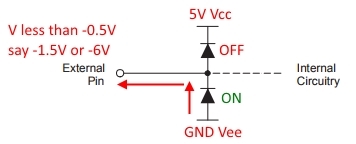

and with R128=0, the PIN3 will be around -6V, and when they change R128 to 200 Ohm, PIN3 will get to around -1.5V. as below is the voltage test at PIN3 when change R128 to 200 Ohm.

if they remove the C104, and then the power supply will not dropped. and also the PIN3 will not have negative voltage. but C104 could not be removed.

so need your support on below:

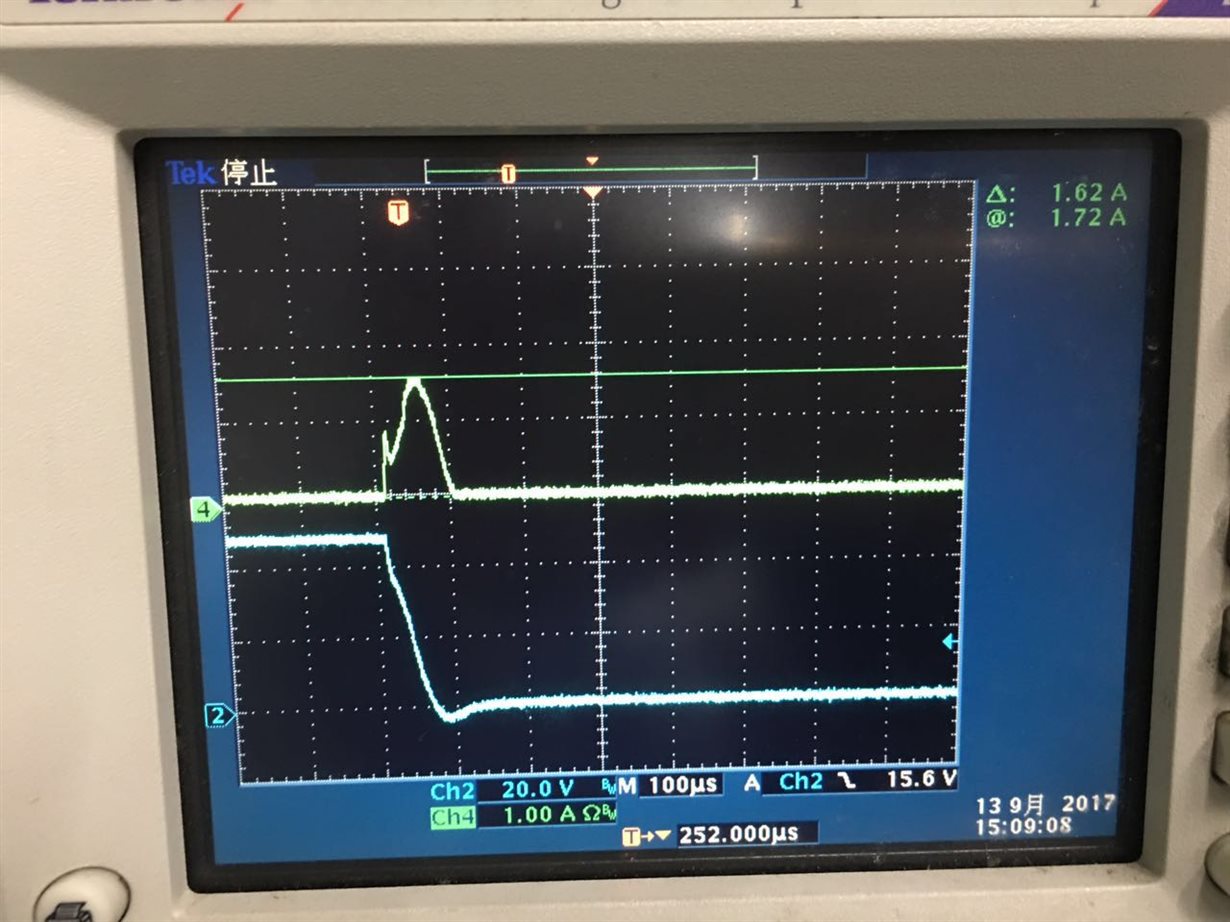

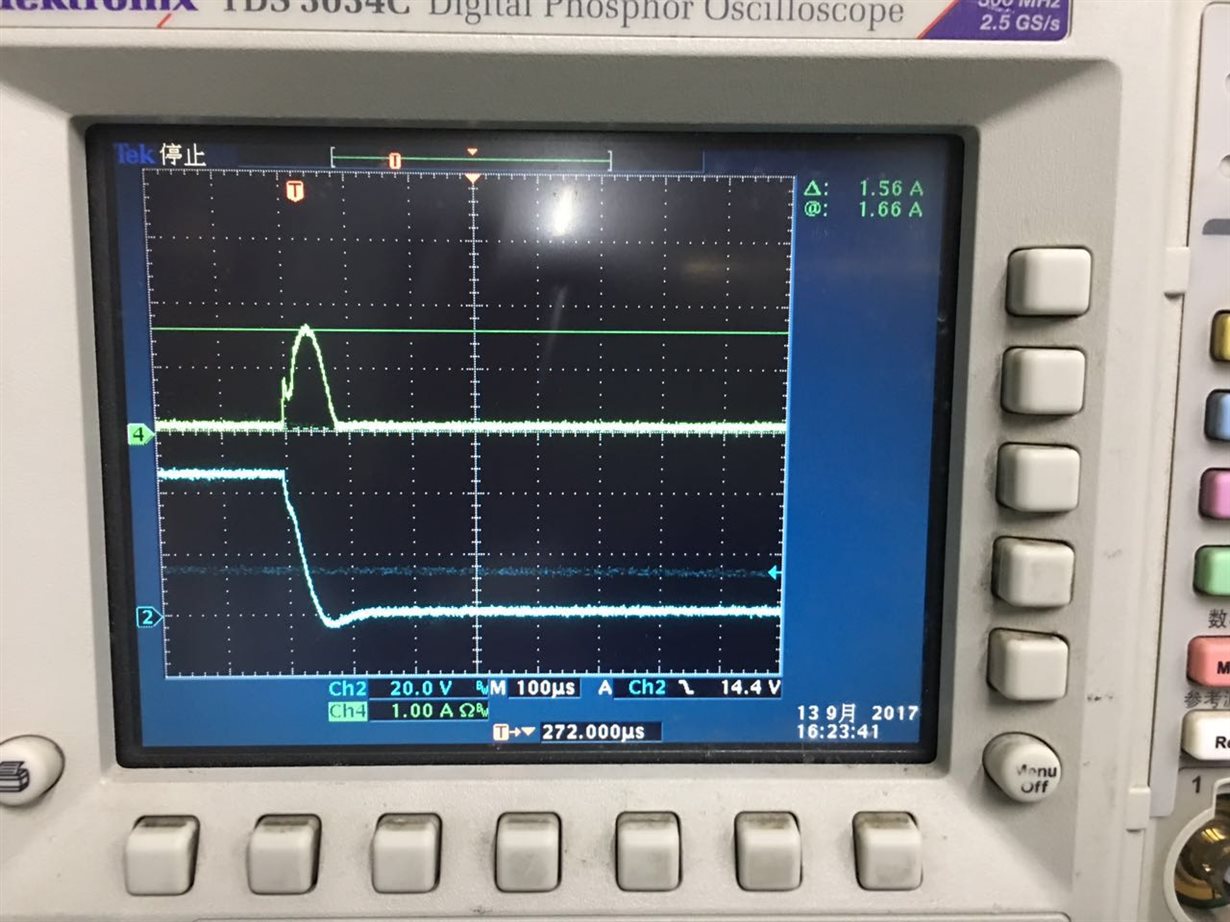

1. what cause the drop of 5V supply? customer thought there is a current pull loop which shown in the red.

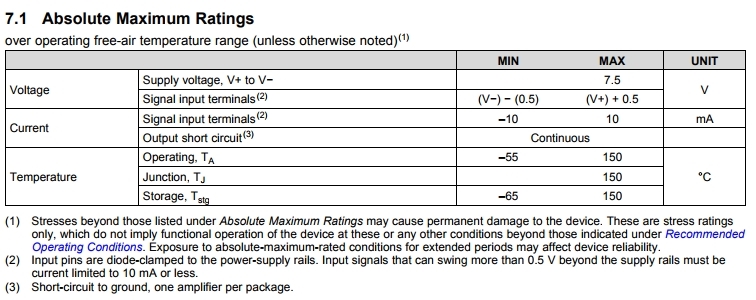

2. because from the d/s, the minimum absolute voltage will be -0.5V with VCC-=0V.pls help evaluate whether there is any risk for such application. so if it could, pls help suggest the solution. (or do you need further information such as the current flow through the pin3 and etc to judge whether it could cause damage?)

tks a lot~!