Hi,

I am working on a differential probe with a the first opamp stages being OPA859's. The input common mode capacitance is said to be 0.62pF.

I could not find any reference regarding any change of that capacitance based on biasing or frequency etc.

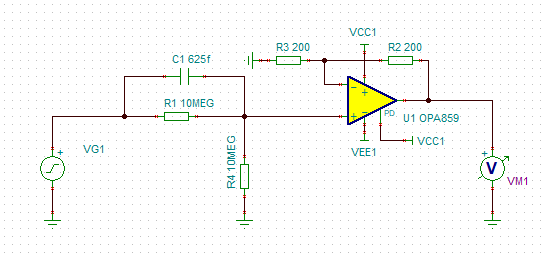

Please consider this schematic:

This forms a 0dB buffer stages with a flat response up to the point where BW starts falling (~730MHz @ -3dB)

Any change on the input common mode capacitance of the opamp would destroy the flatness of the frequency response that i see.

So, does the input common mode capacitance stay the same?

FYI: TSC file

Regards

Manos Tsachalidis