Other Parts Discussed in Thread: OPA2376

Hello Experts,

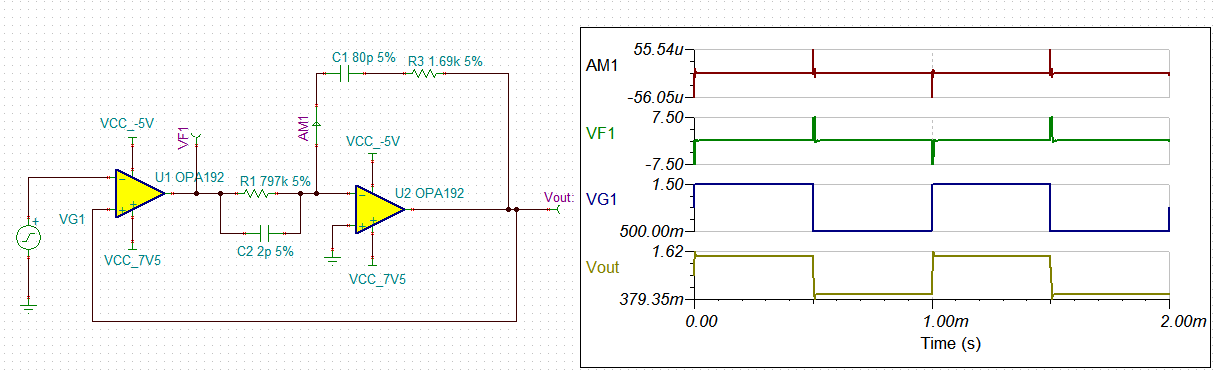

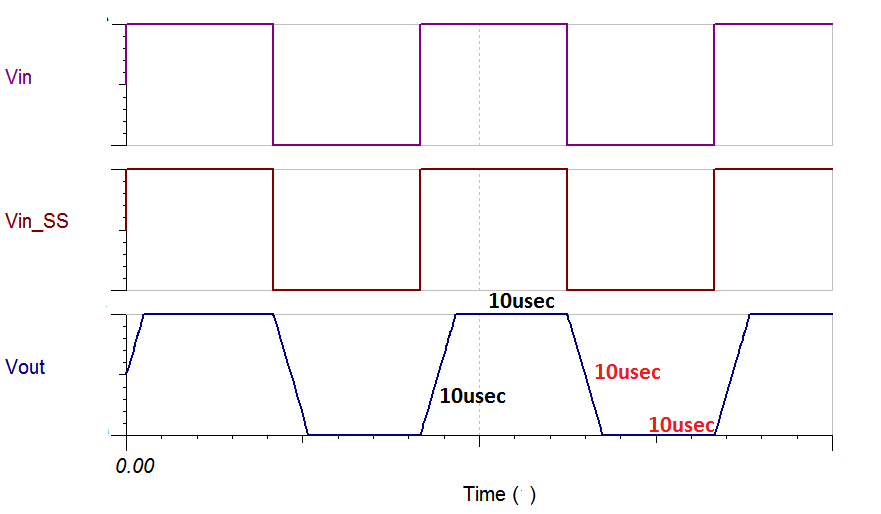

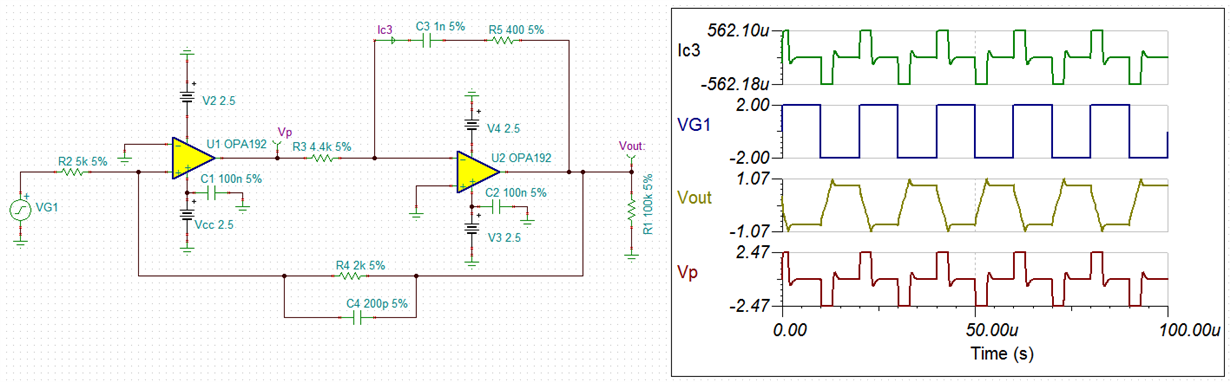

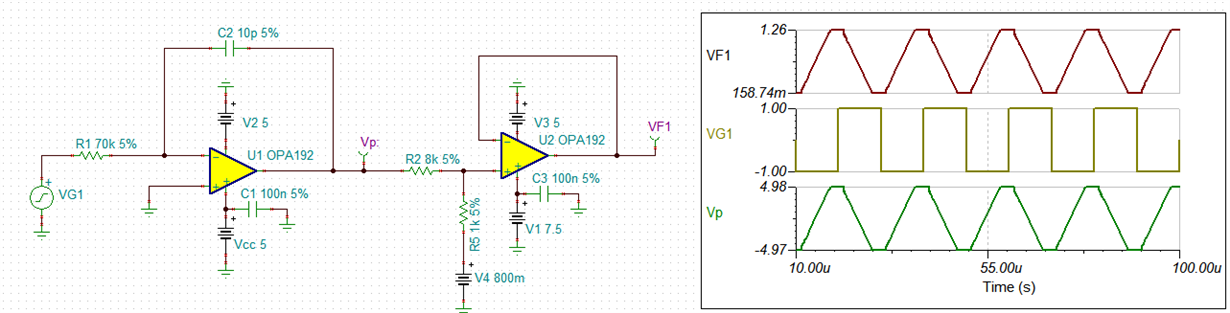

I want to design a voltage buffer with a slew rate limiter. I am referring the below document for my design.

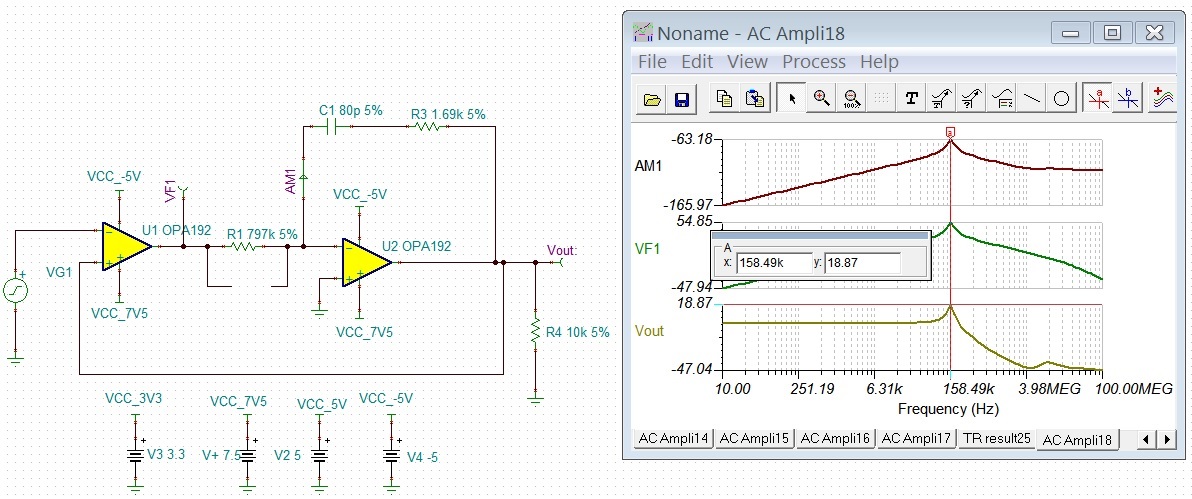

Now In this design, I_C1 is considered as 10uA and Saturation voltage as 10mV. where did these values come from? the example shows a design of 20V/Sec.

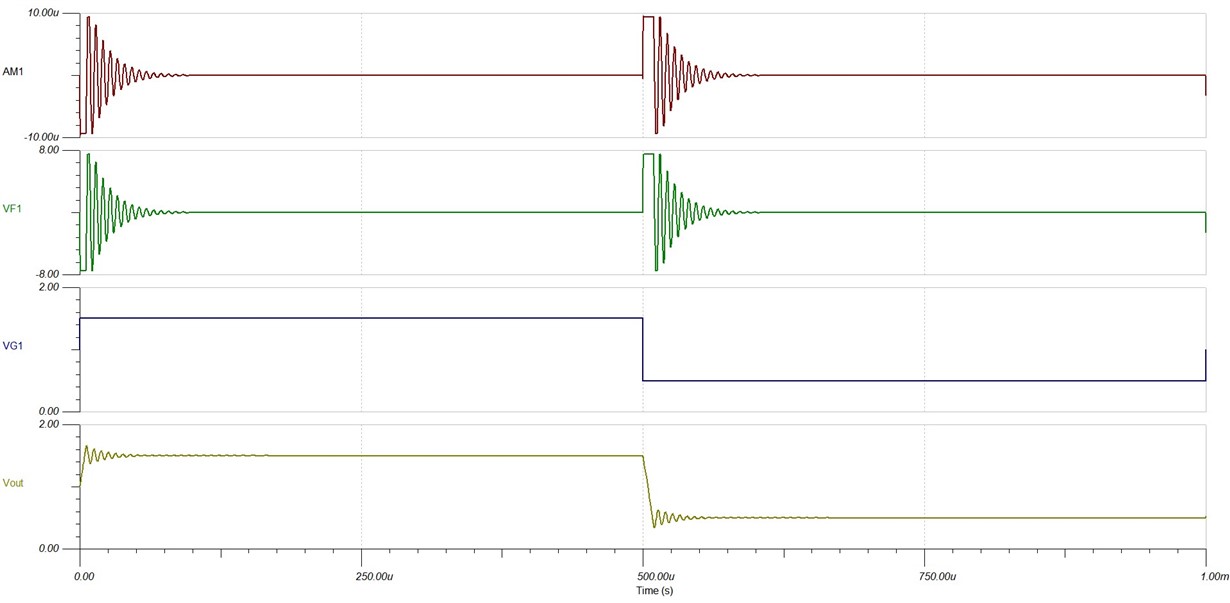

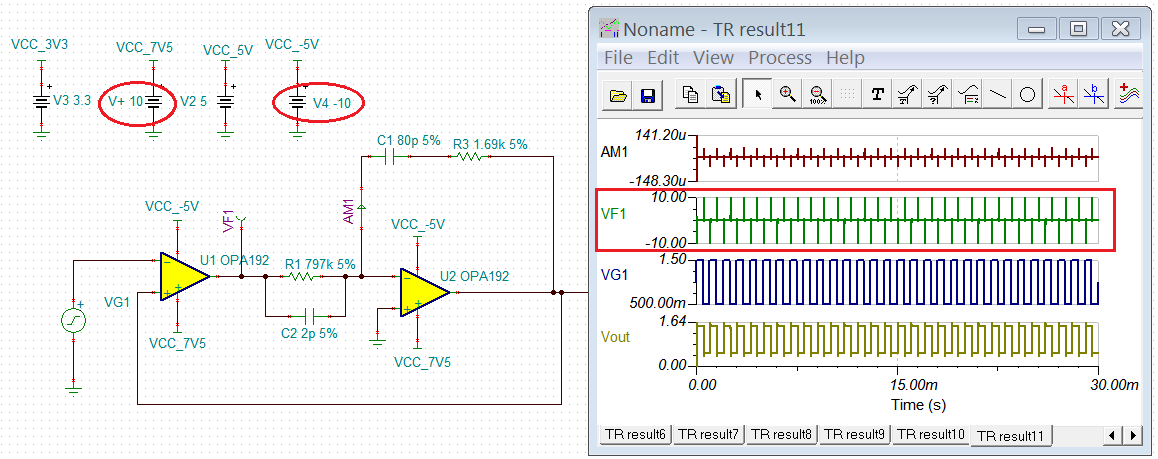

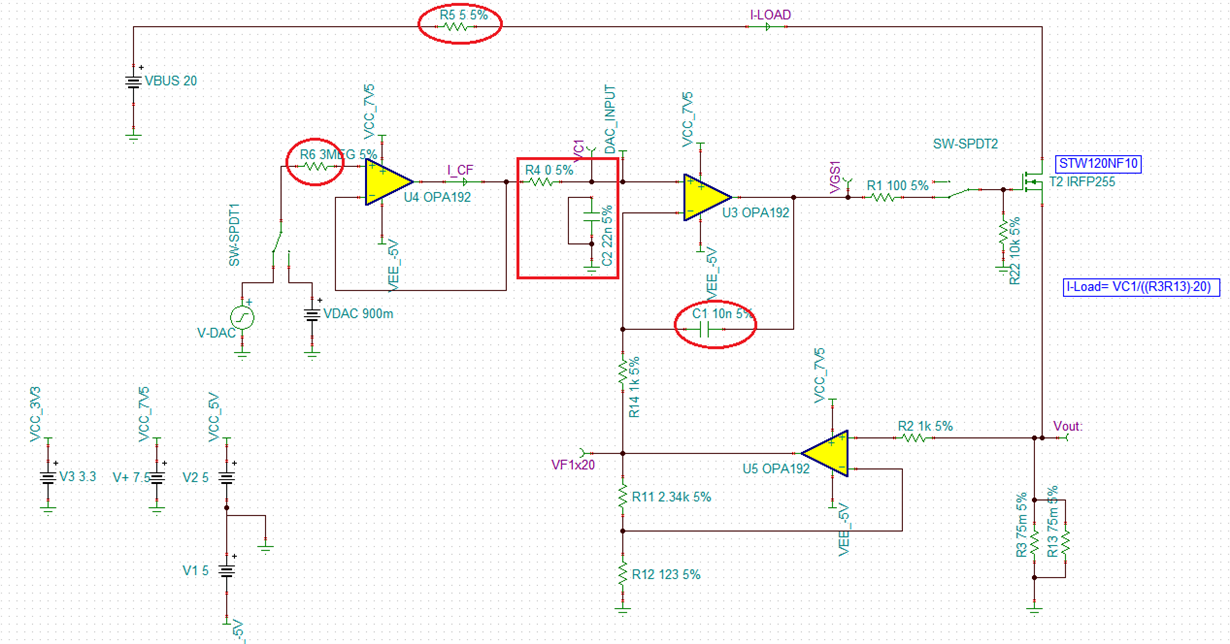

My requirement is 115KV/Sec. I need an adjustable rise depending on my requirement and cannot use a fixed slew rate opamp. Now when I follow the steps and calculate the values, My circuit is ringing. Can you help me with detailed steps in selecting all the components for the desired slew rate?

Thanks

Vishal