Other Parts Discussed in Thread: INA282, LM4041-N, TPS735, , TIDA-00909

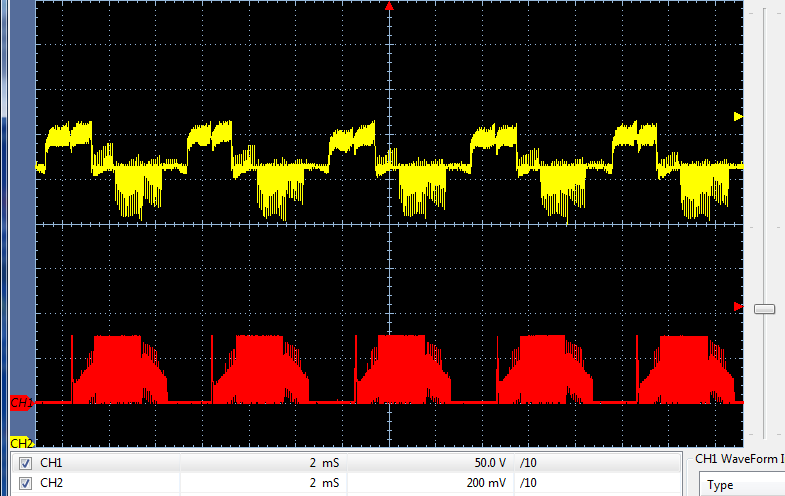

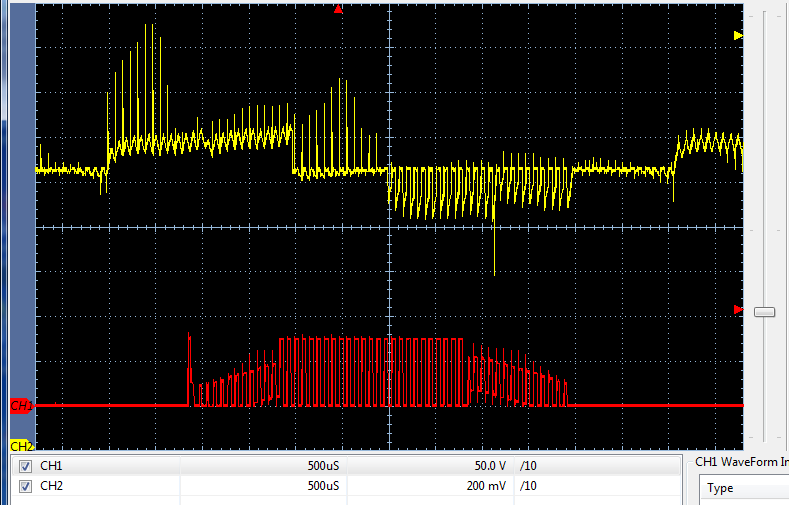

We are using the INA240-A2 in low side monitoring with +3v3 VS and the output is not symmetrical with trapezoidal waveforms being monitored. The PWM noise reduction seems better than INA282 in the same test circuit. Yet it would seem PWM rejection is not rejecting any such thing as 12.5Khz PWM pulses are very present on the output. It would also seem datasheets transient analysis differential IN+/- pins using a sine wave does not prove PWM rejection is even possible. Why datasheet have no graphs showing actual PWM rejection on output as only a square wave IN+/-, not an actual PWM signal to prove rejection?

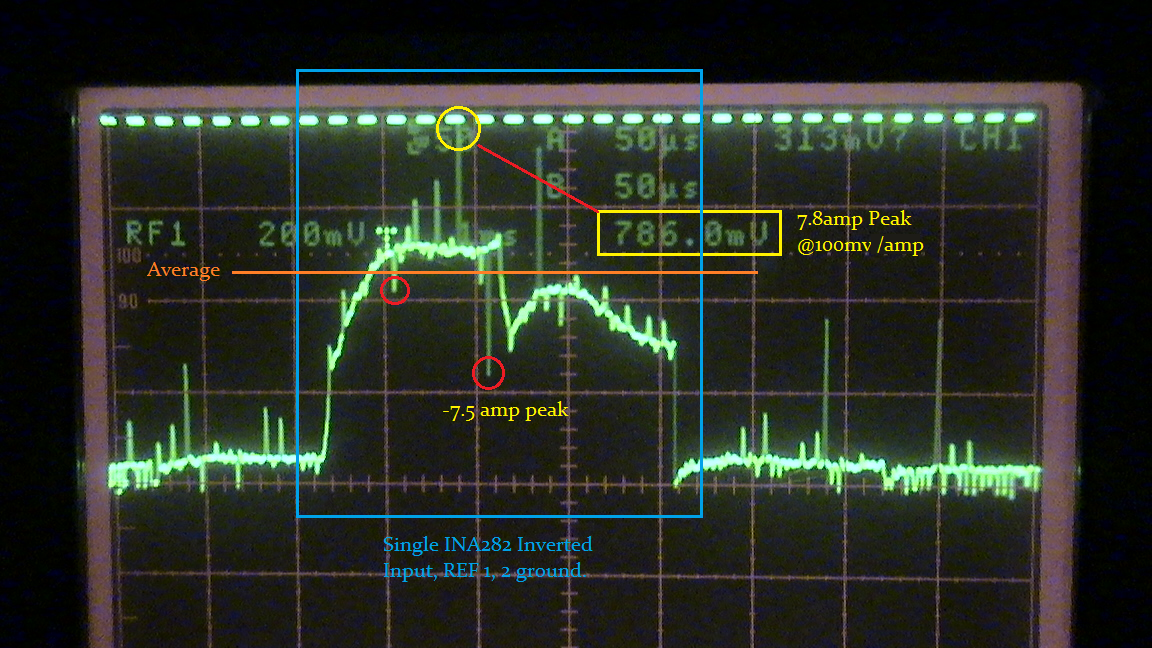

Forward positive current flow produces a somewhat monotonic output rise using 1.225v precision reference LM4041-N, REF1/2 tied together. It seems it can not produce a proper ratio metric or linear output rise from negative current thus produce (single) pulses in opposition to forward current having rise from 0v up to trapezoidal positive current peaks. The output signal losses symmetry when the PWM duty cycle rises above 25%. So differential amplifier bandwidth seems to increase in gain/db relative Figs. 10/12 for PWM frequencies 12.5Khz up to 40Khz. Tina transient analysis looks nothing like the output signal being produced.

Previous testing circuits gave doubt of any proclaimed PWM rejection, we opted to add Johanson ceramic EMI decoupling cap XY2 1nf filtering on IN+/-. They made no difference in number of PWM pulses appearing on the output or the output gain exceeding well over 50 via 0.5uohm shunts. Whereas a 150 volt PWM pulse can easily produce outputs exceeding +/-2 up to +/-4v even tough VS pin has dedicated +3v3 regulator TPS735, VS pin 4.7uf/0.1uf bypass.

Why is there NO PWM rejection on low side monitoring and how can the A2 gain seem to exceed 50mv/A steady state duty cycles? Also seems excessive A2 gain error present, perhaps gain was not set properly at the factory or varies depending on the input signal type? What can we do to make the signal symmetry mirrored where SAR ADC can more easily determine ratio metric linear current rise in the PWM duty cycle?