Other Parts Discussed in Thread: TINA-TI, , TL064, TL074, LM324, OP27

Hi!

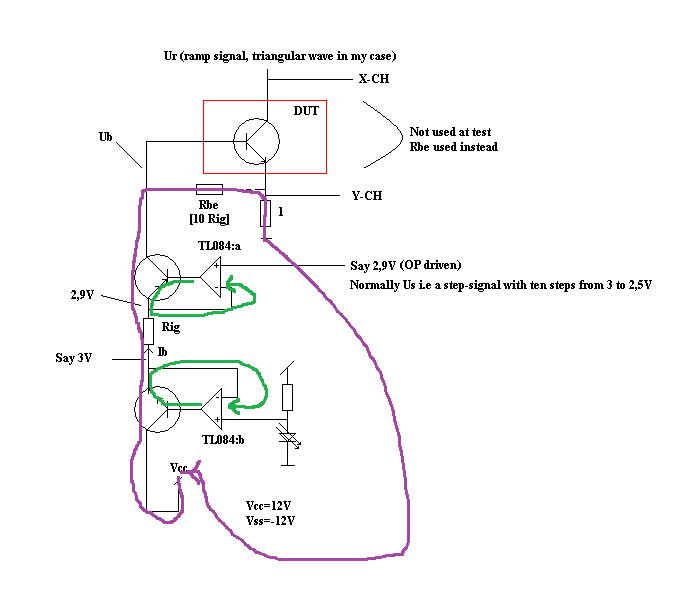

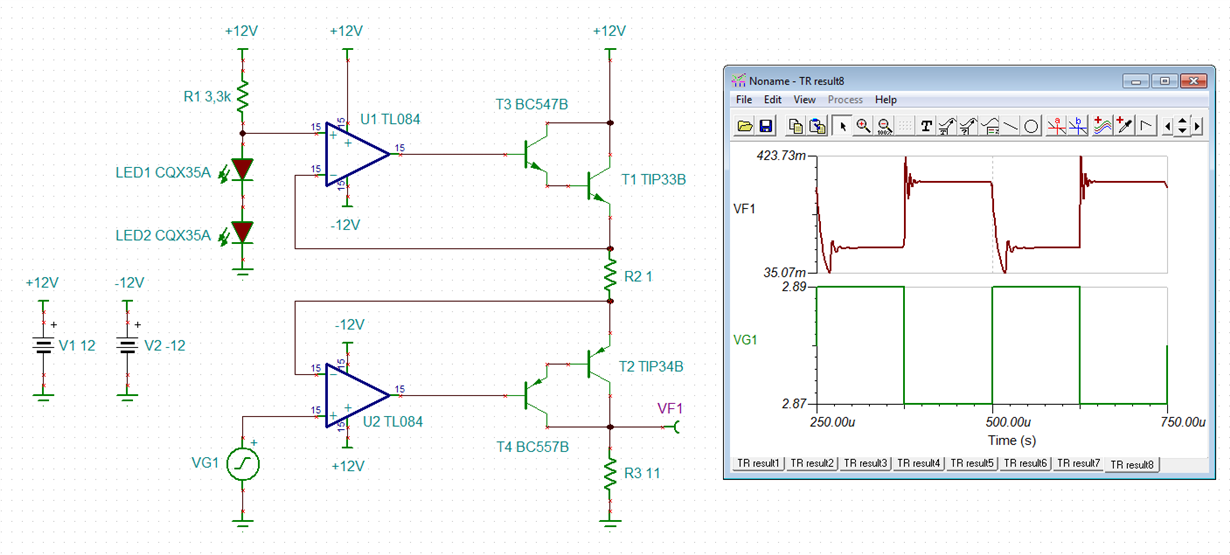

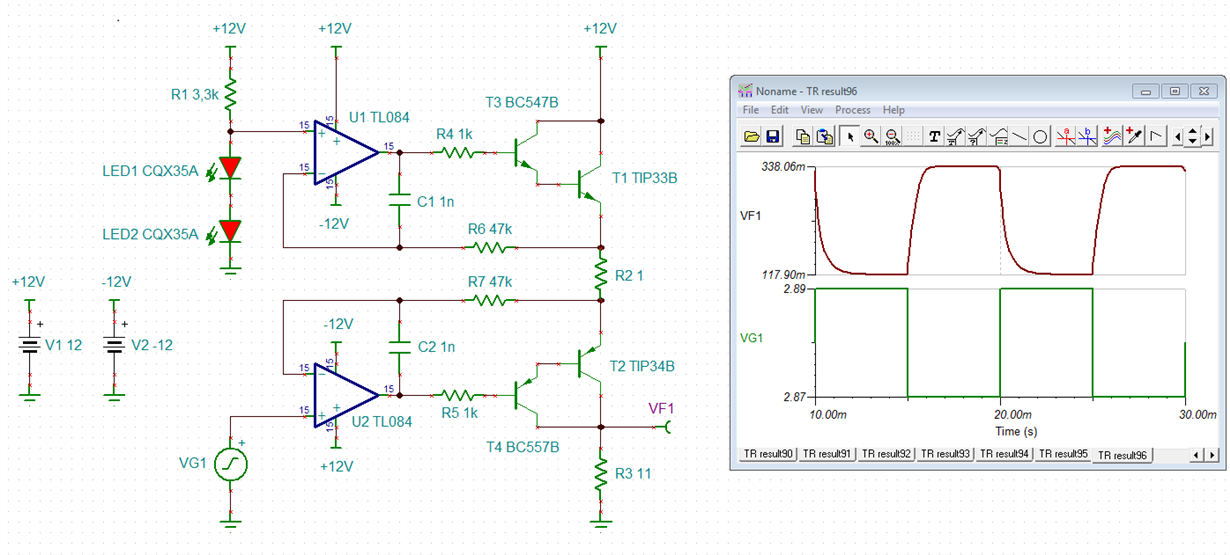

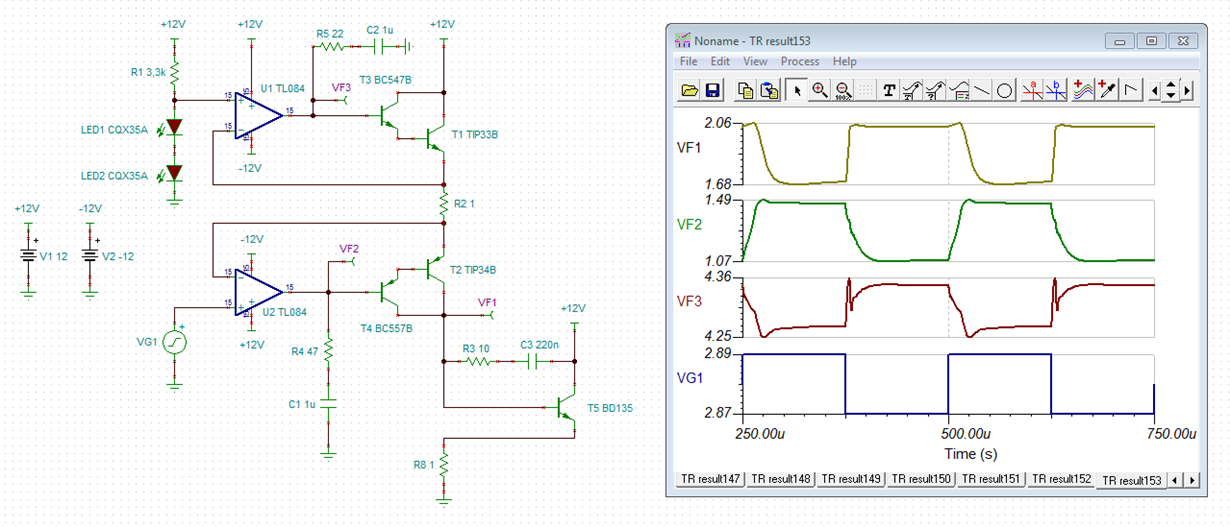

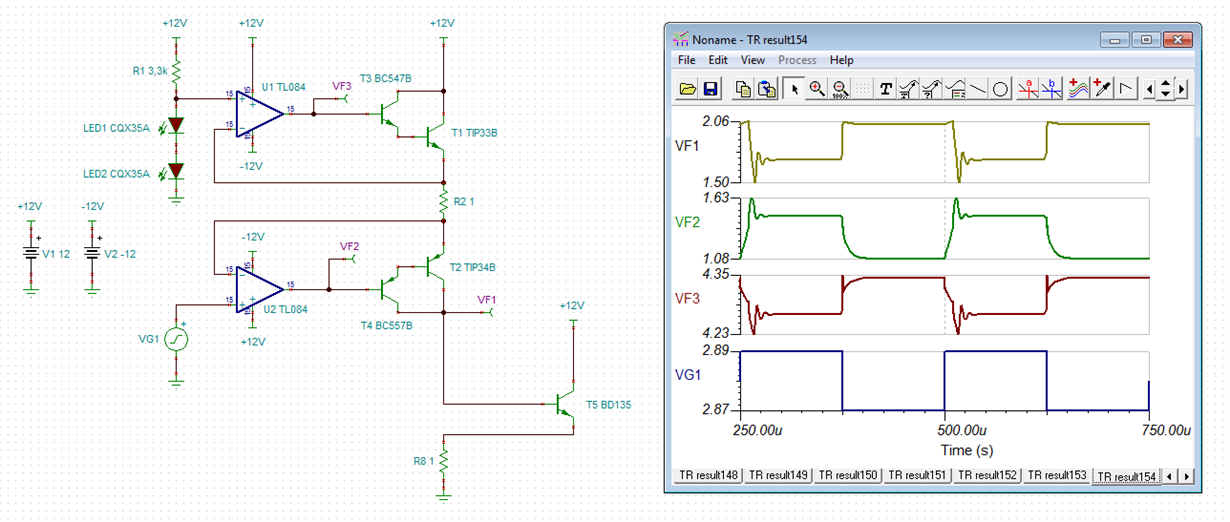

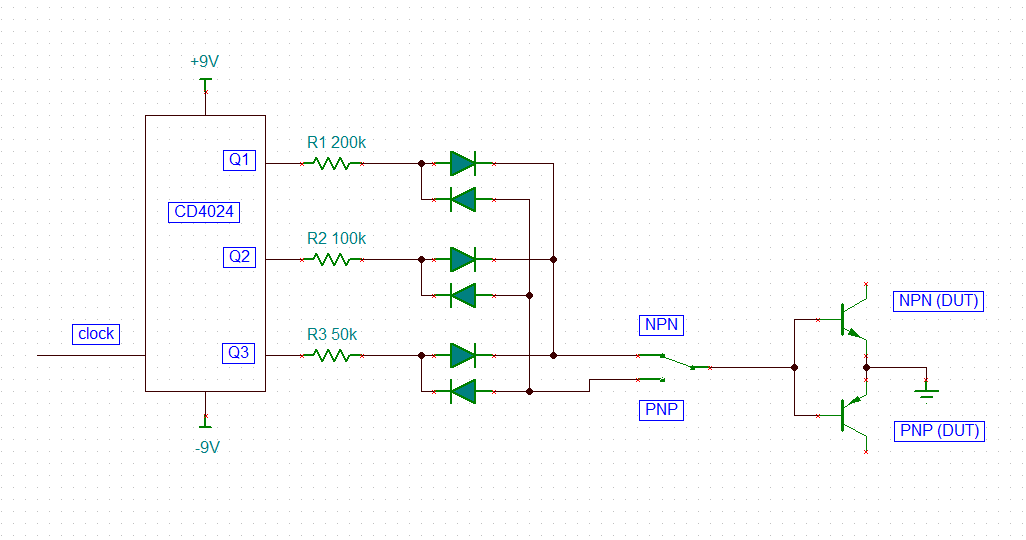

I am trying to build a transistor curve tracer but at some settings I get stubborn oscillations that I really can't get rid of.

I think that HF-oscillations should be quite "easy" to get rid of, it usually just takes a small capacitor at the right place.

However, I have tried for weeks now to find that certain place.

The oscillations occur at Ub (and actually almost everywhere but it is there I measure it).

Now, using a Rig of 1k makes things work without oscillations but using Rig of 1 Ohms makes it oscillate.

I really need 1 Ohms to be able to test high power transistors (up to 5 amps momentarilly is my thought).

So why does it oscillate with Rig of 1 Ohms and not with Rig of 1k?

I have almost given up on this project.

MVH/Roger

PS

To me it seems like it is current dependent but how can a certain amount of current make things unstable?

I seem not to be able to move the picture to where i want it, I am bad with computers.