Part Number: TLV6001

Other Parts Discussed in Thread: TINA-TI

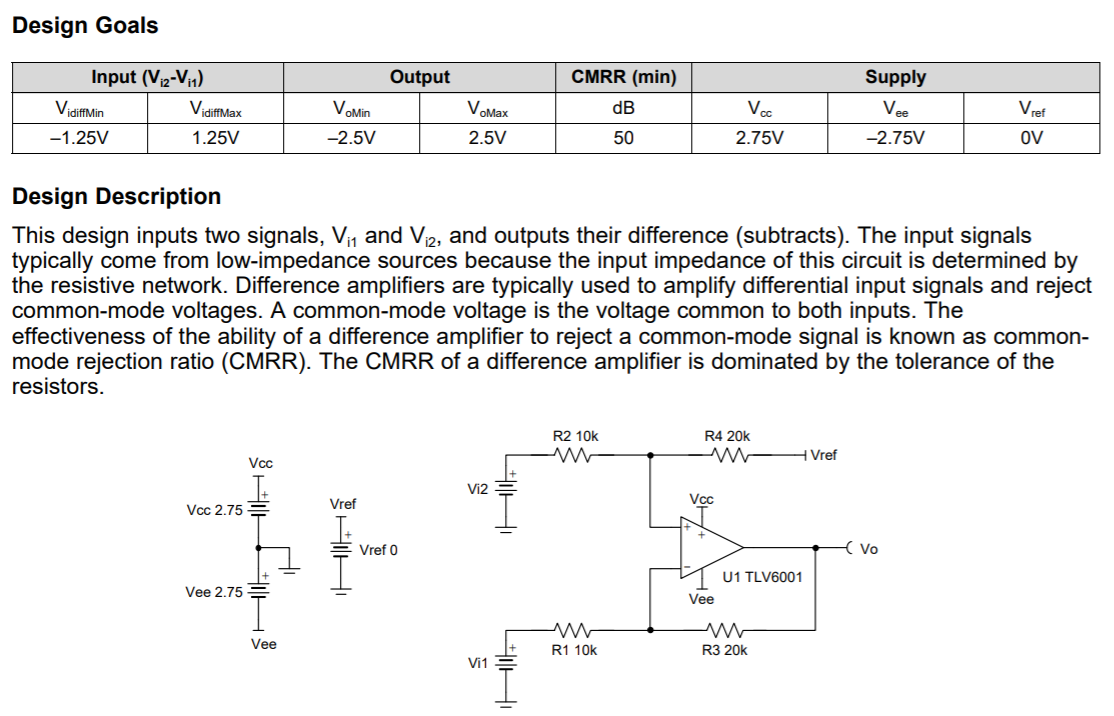

Hello, when i read the book <<Analog Engineer’s Circuit Cookbook: Amplifiers>> by TI at Page 23rd,

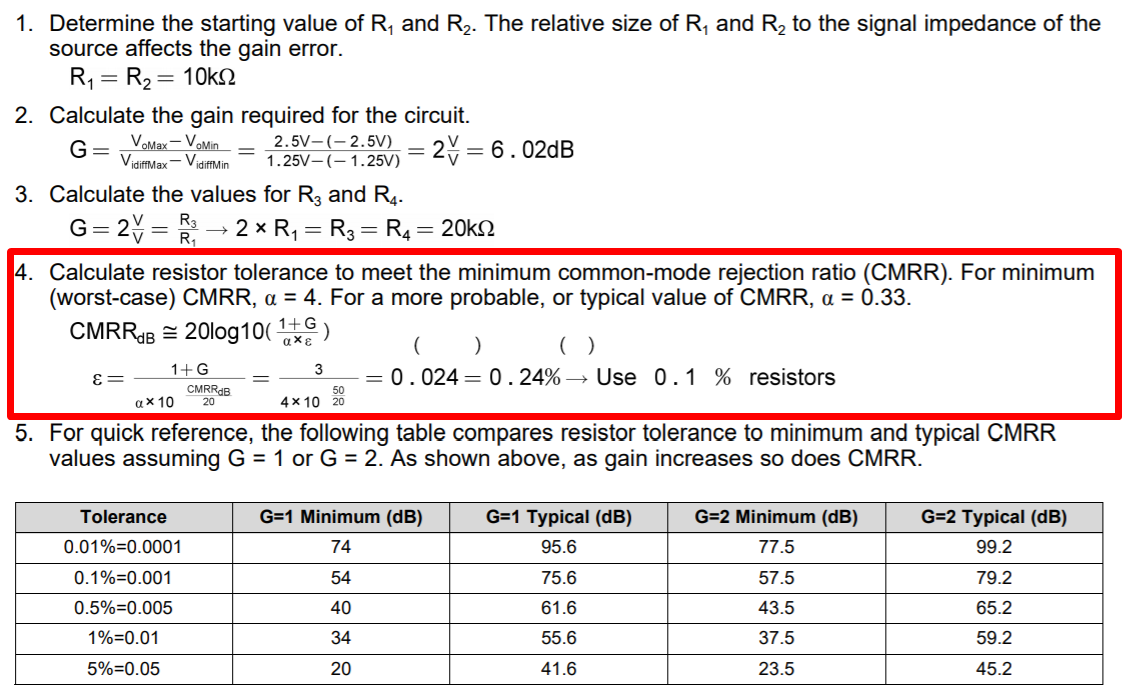

Q1: They said that Calculating resistor tolerance to meet the minimum CMRR at "Difference amplifier (subtractor) circuit"(see fig 1) by using the way in fig.2 and i do not know that formula came from?

Q2:I konw the CMRR=Aud/Auc, and Aud means the gain of different signal and Auc means gain of common mode signal. And in datasheet of OPA, CMRR= 20 x log(dVcm/dVos), and Vcm is common mode input and Vos means input offset voltage, and the value is internal parameter. But in fig1, the CMRR is NOT the CMRR= 20 x log(dVcm/dVos), and in fig.1 Vo=Aud x Vdiff + Auc x Vcm, and CMRR= Aud/Auc, which is not related to Vos caused by Vcm, and Aud and Auc is determined by External Rrsistor.

More, Vos is smaller than Vdiff (Vdiff=Vi2 - Vi1). So is it true that I say the different CMRR? and Why CMRR in fig.1 is not the parameter in OPA datasheet?

fig 1 Difference amplifier (subtractor) circuit

fig.2 calculation of the resistor