Hi,

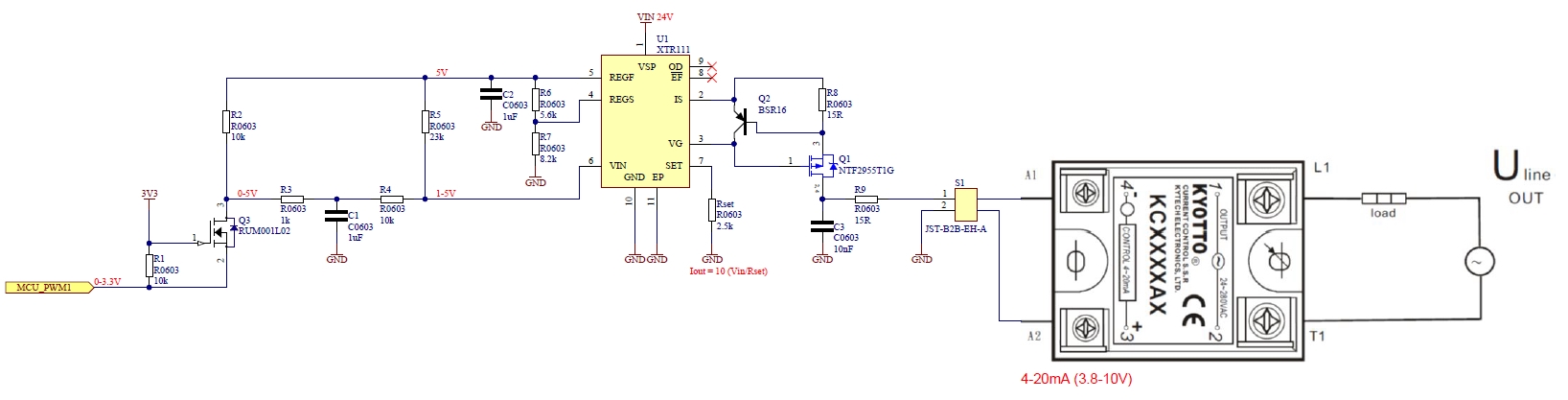

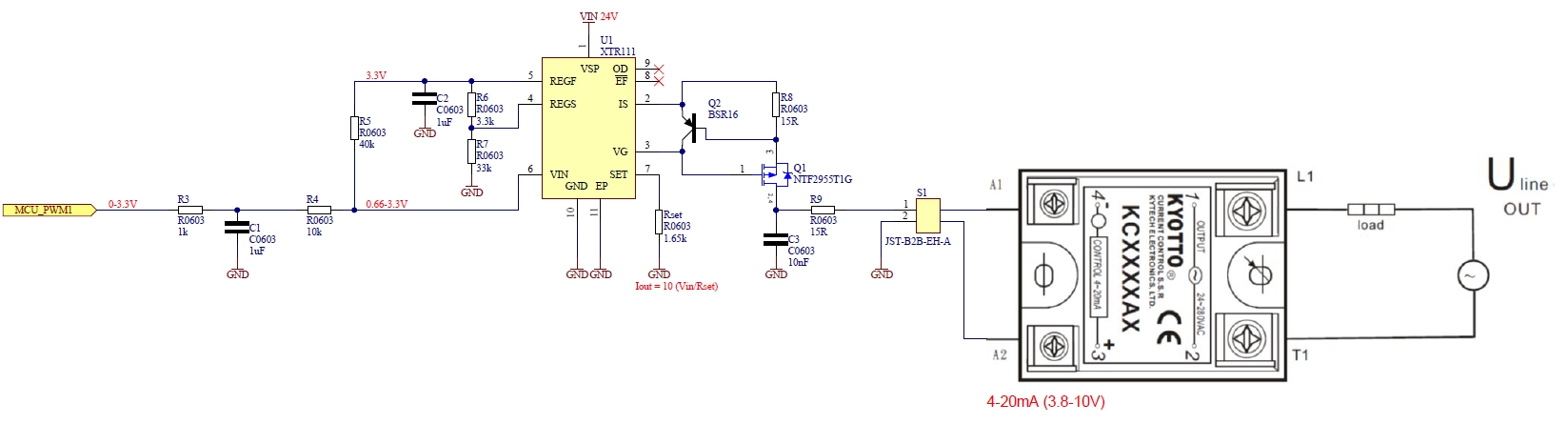

I Want to control a solid state relay (SSR) from my MCU. The SSR is controlled by 4-20mA (3.8-10V). I want to use the XTR111 and a PWM output from my MCU. R3 and C1 are supposed to filter the PWM to a DC voltage for the XTR111's VIN. I have no experience with XTR111 or designing 4-20mA circuits.

Will this work?