Hi:

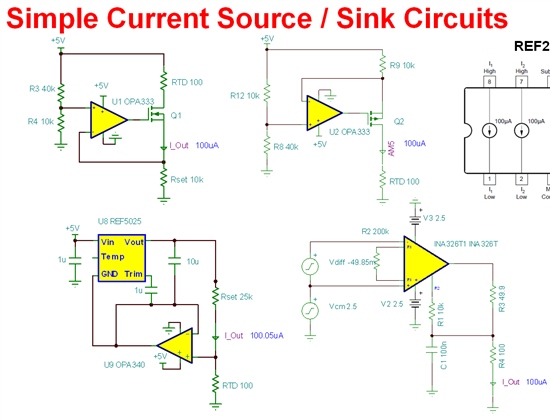

I saw this precision current sink from this app note :http://www.ti.com/sc/docs/psheets/abstract/apps/snla140a.htm (page 13) and i'm trying to understand its behavior.

What is re purpose of the NPN transistor. I understand the basic OPAMP + FET as a current source but what makes the addition of ths NPN a precision current source. if i understand the circuit right, the NPN will turn on once a current of 60uA or greater is sourced into the load , i.e assuming a Vbe of 0.6V, the NPN will be on for currents of (0.6V / 10K) or greater. Does this mean that for lower current levels, the NPN isn't linear or reliable?

I'm seekling a precision sink capable of sinking currents from 1uA to 5mA with an accuracy of 10nA or less. Will this circuit perfrom the task? I know the basic OPAMP+FET will not as its not linear for low currents.

Please anyone help if you can...

Also, i'm plannign to change Q1 to an N-channel MOSFET. Would that be ok as well?

Thanks!

David

.

.