Other Parts Discussed in Thread: OPA335

Hi Team,

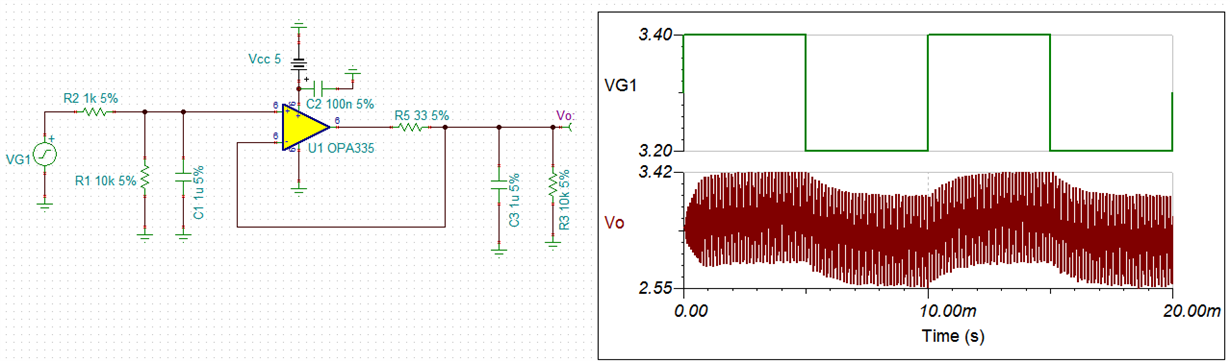

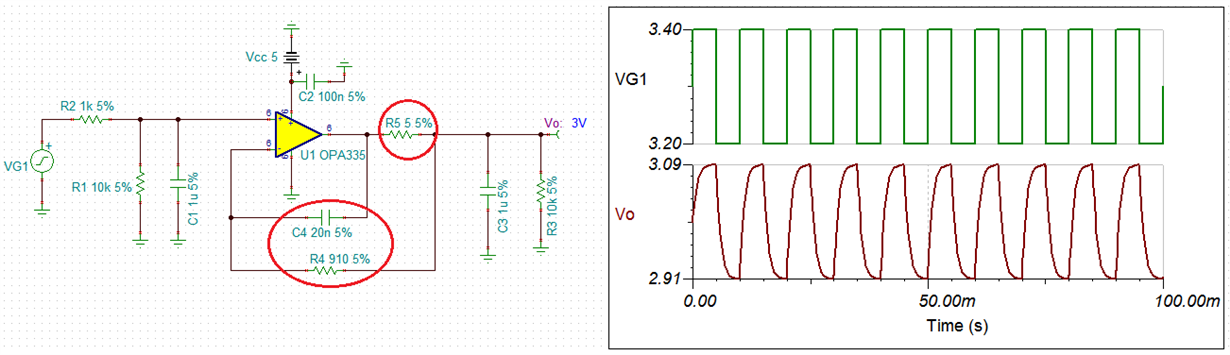

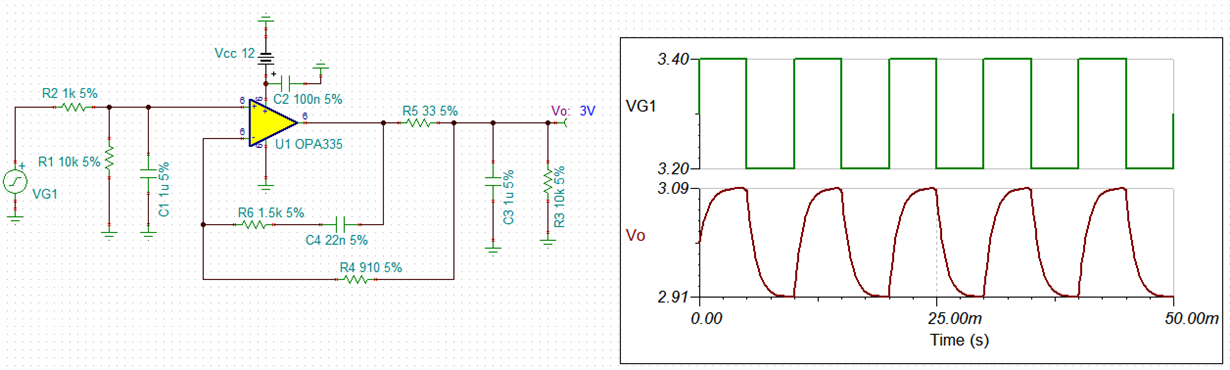

My customer used OPA2335 which always reported EOS damage, the OPA2335 Input is 3.3V, which used to generate 3V, and the 3V is used for ADC sensing clamp. This is for UPS application.

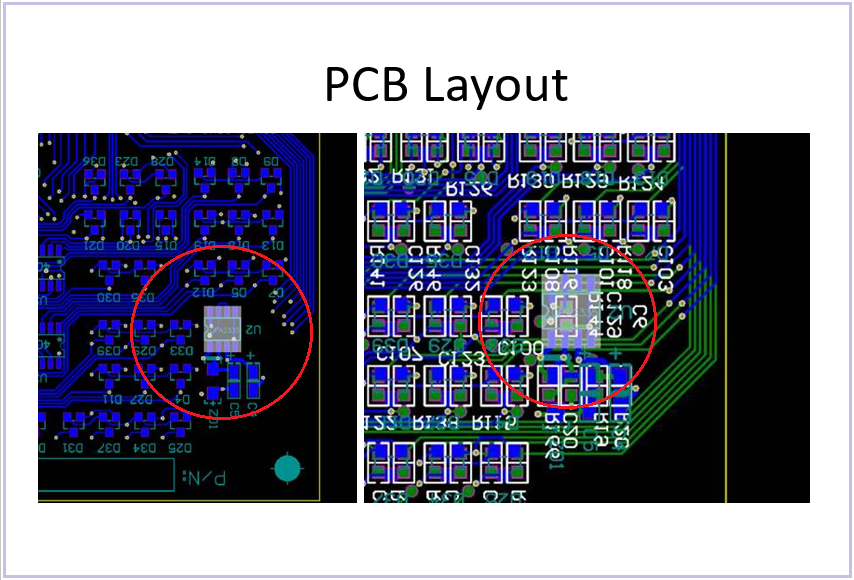

Could you kindly review the schematic and PCB layout, and give comments on how the EOS come and how to avoid? the schematic and PCB layout shown as attached file.

Expect for your kindly reply, thanks.OPA2335 Issue.pptx

Best Regards

Benjamin