We have successfully configured the Audio codec as per the suggestion provided by TI and the link as given below

Currently we are facing other issues with respect to playback speed.

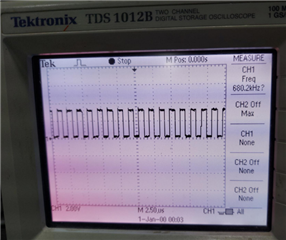

Problem statement : The playback speed in TLV320AIC31xx is at half the speed of what is expected. We expect it to happen in 1x speed but the playback speed happening in 0.5x.

i have changed the frequencies up to clock-frequency = <19200000> in the DTS file, but the problem is not yet solved. Only we are facing the issues in TLV320AIC31xx audio codec, also i have tried with wm9860, everything working good.

So, i need your support to resolve this playback setting issues in the TLV320AIC31xx at driver level.

Regards

Ravi V