Hi Team,

I have a question about PCM1801 I2S format.

[32-BCK/LRCK]

Datasheet page14 "SERIAL AUDIO DATA INTERFACE" describes "PCM1801 accepts the 64-BCK/LRCK or 48-BCK/LRCK format (only for a 384-fS system clock) for I2S format.".

When I take a look at Figure 25. Audio Data Format, it seems PCM1801 supports 32-BCK/LRCK but why PCM1801 doesn't accept 32-BCK/LRCK?

I2S protocol actually includes a 1 BCLK cycle delay between the LRCK edge and the start of data, so in other words can we say PCM1801 accepts the 32 + 2 BCK/LRCK for I2S format?

[POWER-ON RESET]

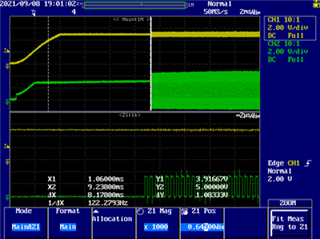

it is difficult to follow figure 24. internal power-on reset timing especially "the system clock must be supplied as soon as power is applied; more specifically, the device must receive at least three system clock cycles before VDD > 4 V. While VCC/VDD < 4 V (typical)".

Customer power up sequence is below.

wait approx. 7ms after 5V supplies then system clock supplies.

Question here is

#1: Are there any concern about this power up sequence?

#2: In below power up sequence with I2S mode, when should we set FMT to "H"? after 1024 system clocks from first edge?

Regards,

Kai