Other Parts Discussed in Thread: TLV320AIC3106

Dear Team,

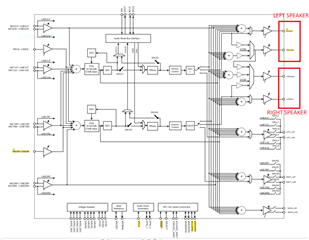

We are using TLV320AIC31106 codec for our project. As per the project we had connected two speakers in left channel connected one speaker and right other one.

As per our project we need shift one speaker to another as per the situation (Phone application Handset and Handsfree), I had tried to mute the LFET and Right DAC channel in the Table 51. Page 0 / Register 43: Left DAC Digital Volume Control Register on fly.

Read the register it is applying the values are not, its updated but not muted. So please provide your inputs to switch from one channel to other without disturbing the audio.

Please find the configuration details and diagram.

tlv320_codec configparam_tlv [] = {

{AIC3106_REG0_PAGESELECT, 0x00},

{AIC3106_REG0_RESET, 0x80},

{AIC3106_REG0_CODEC_SAMPLE_RATE, 0xAA},

{AIC3106_REG0_PLL_A, 0x10},

{AIC3106_REG0_PLL_B, 0x00},

{AIC3106_REG0_PLL_C, 0x00},

{AIC3106_REG0_PLL_D, 0x00},

{AIC3106_REG0_CODEC_DATAPATH, 0x0A},

{AIC3106_REG0_SERIAL_DATA_INTFC_A, 0xF0},

{AIC3106_REG0_SERIAL_DATA_INTFC_B, 0x00},

{AIC3106_REG0_SERIAL_DATA_INTFC_C, 0x08},

{AIC3106_REG0_OVERFLOW_FLAG, 0x00},

{AIC3106_REG0_DIG_FILTER_CNTL, 0x00},

{AIC3106_REG0_HEADSET_BUTTON_PRESS_A,0x00},

{AIC3106_REG0_HEADSET_BUTTON_PRESS_B,0x00},

{AIC3106_REG0_LEFT_ADC_PGA, 0x00},

{AIC3106_REG0_RIGHT_ADC_PGA, 0x00},

#if I2S_PATH_REQD

{AIC3106_REG0_MIC3LR_LEFT_ADC, 0xF0},

{AIC3106_REG0_MIC3LR_RIGHT_ADC, 0xF0},

{AIC3106_REG0_LINE1L_LEFT_ADC, 0x7C},

#else

{AIC3106_REG0_MIC3LR_LEFT_ADC, 0x00},

{AIC3106_REG0_MIC3LR_RIGHT_ADC, 0x00},

{AIC3106_REG0_LINE1L_LEFT_ADC, 0x00},

#endif

{AIC3106_REG0_LINE2L_LEFT_ADC, 0x00},

{AIC3106_REG0_LINE1R_LEFT_ADC, 0x00},

#if I2S_PATH_REQD

{AIC3106_REG0_LINE1R_RIGHT_ADC, 0x7C},

#else

{AIC3106_REG0_LINE1R_RIGHT_ADC, 0x00},

#endif

{AIC3106_REG0_LINE2R_RIGHT_ADC, 0x00},

{AIC3106_REG0_LINE1L_RIGHT_ADC, 0x00},

{AIC3106_REG0_MICBIAS, 0x40},

{AIC3106_REG0_LEFT_AGC_CNTL_A, 0x00},

{AIC3106_REG0_LEFT_AGC_CNTL_B, 0x00},

{AIC3106_REG0_LEFT_AGC_CNTL_C , 0x00},

{AIC3106_REG0_RIGHT_AGC_CNTL_A, 0x00},

{AIC3106_REG0_RIGHT_AGC_CNTL_B, 0x00},

{AIC3106_REG0_RIGHT_AGC_CNTL_C, 0x00},

{AIC3106_REG0_LEFT_AGC_GAIN, 0x00},

{AIC3106_REG0_RIGHT_AGC_GAIN, 0x00},

{AIC3106_REG0_LEFT_AGC_NOISE_GATE, 0x00},

{AIC3106_REG0_RIGHT_AGC_NOISE_GATE, 0x00},

{AIC3106_REG0_ADC_FLAG, 0x00},

#if I2S_PATH_REQD

{AIC3106_REG0_DAC_POWER_OUTPUT_DRVR, 0xE0},

{AIC3106_REG0_HI_POWER_OUTPUT_DRVR, 0x00},

#else

{AIC3106_REG0_DAC_POWER_OUTPUT_DRVR, 0x00},

{AIC3106_REG0_HI_POWER_OUTPUT_DRVR, 0x00},

#endif

{AIC3106_REG0_RESERVED_39, 0x00},

{AIC3106_REG0_HI_POWER_OUTPUT_CNTL, 0x00},

{AIC3106_REG0_DAC_OUTPUT_SWITCHING, 0x00},

{AIC3106_REG0_OUTPUT_POP_REDUCTION, 0x00},

{AIC3106_REG0_LEFT_DAC_VOLUME, 0x00},

{AIC3106_REG0_RIGHT_DAC_VOLUME, 0x00},

{AIC3106_REG0_LINE2L_TO_HPLOUT, 0x00},

#if MIC_SPKR_LOOP_BACK

{AIC3106_REG0_PGA_L_TO_HPLOUT, 0x80},

#else

{AIC3106_REG0_PGA_L_TO_HPLOUT, 0x00},

#endif

#if I2S_PATH_REQD

{AIC3106_REG0_DAC_L1_TO_HPLOUT, 0x80},

#else

{AIC3106_REG0_DAC_L1_TO_HPLOUT, 0x00},

#endif

{AIC3106_REG0_LINE2R_TO_HPLOUT, 0x00},

#if MIC_SPKR_LOOP_BACK

{AIC3106_REG0_PGA_R_TO_HPLOUT, 0x80},

#else

{AIC3106_REG0_PGA_R_TO_HPLOUT, 0x00},

#endif

{AIC3106_REG0_DAC_R1_TO_HPLOUT, 0x00},

{AIC3106_REG0_HPLOUT_OUTPUT_LEVEL, 0x09},

{AIC3106_REG0_LINE2L_TO_HPLCOM, 0x00},

{AIC3106_REG0_PGA_L_TO_HPLCOM, 0x00},

{AIC3106_REG0_DAC_L1_TO_HPLCOM, 0x00},

{AIC3106_REG0_LINE2R_TO_HPLCOM, 0x00},

{AIC3106_REG0_PGA_R_TO_HPLCOM, 0x00},

{AIC3106_REG0_DAC_R1_TO_HPLCOM, 0x00},

{AIC3106_REG0_HPLCOM_OUTPUT_LEVEL, 0x00},

{AIC3106_REG0_LINE2L_TO_HPROUT, 0x00},

{AIC3106_REG0_PGA_L_TO_HPROUT, 0x00},

{AIC3106_REG0_DAC_L1_TO_HPROUT, 0x00},

{AIC3106_REG0_LINE2R_TO_HPROUT, 0x00},

{AIC3106_REG0_PGA_R_TO_HPROUT, 0x00},

#if I2S_PATH_REQD

{AIC3106_REG0_DAC_R1_TO_HPROUT, 0x80},

#else

{AIC3106_REG0_DAC_R1_TO_HPROUT, 0x80},

#endif

{AIC3106_REG0_HPROUT_OUTPUT_LEVEL, 0x09},

{AIC3106_REG0_LINE2L_TO_HPRCOM, 0x00},

{AIC3106_REG0_PGA_L_TO_HPRCOM, 0x00},

{AIC3106_REG0_DAC_L1_TO_HPRCOM, 0x00},

{AIC3106_REG0_LINE2R_TO_HPRCOM, 0x00},

{AIC3106_REG0_PGA_R_TO_HPRCOM, 0x00},

{AIC3106_REG0_DAC_R1_TO_HPRCOM, 0x00},

{AIC3106_REG0_HPRCOM_OUTPUT_LEVEL, 0x00},

{AIC3106_REG0_LINE2L_TO_MONO_LOP, 0x00},

{AIC3106_REG0_PGA_L_TO_MONO_LOP, 0x00},

{AIC3106_REG0_DAC_L1_TO_MONO_LOP, 0x00},

{AIC3106_REG0_LINE2R_TO_MONO_LOP, 0x00},

{AIC3106_REG0_PGA_R_TO_MONO_LOP , 0x00},

{AIC3106_REG0_DAC_R1_TO_MONO_LOP, 0x00},

{AIC3106_REG0_MONO_LOP_OUTPUT_LEVEL, 0x00},

{AIC3106_REG0_LINE2L_TO_LEFT_LOP, 0x00},

{AIC3106_REG0_PGA_L_TO_LEFT_LOP , 0x00},

{AIC3106_REG0_DAC_L1_TO_LEFT_LOP, 0x00},

{AIC3106_REG0_LINE2R_TO_LEFT_LOP, 0x00},

{AIC3106_REG0_PGA_R_TO_LEFT_LOP , 0x00},

{AIC3106_REG0_DAC_R1_TO_LEFT_LOP, 0x00},

{AIC3106_REG0_LEFT_LOP_OUTPUT_LEVEL, 0x00},

{AIC3106_REG0_LINE2L_TO_RIGHT_LOP, 0x00},

{AIC3106_REG0_PGA_L_TO_RIGHT_LOP, 0x00},

{AIC3106_REG0_DAC_L1_TO_RIGHT_LOP, 0x00},

{AIC3106_REG0_LINE2R_TO_RIGHT_LOP, 0x00},

{AIC3106_REG0_PGA_R_TO_RIGHT_LOP, 0x00},

{AIC3106_REG0_DAC_R1_TO_RIGHT_LOP, 0x00},

{AIC3106_REG0_RIGHT_LOP_OUTPUT_LEVEL,0x00},

{AIC3106_REG0_MODULE_POWER_STATUS, 0x00},

{AIC3106_REG0_OUTPUT_SHORT_CIRCUIT, 0x00},

{AIC3106_REG0_STICKY_IRQ_FLAGS, 0x00},

{AIC3106_REG0_REALTIME_IRQ_FLAGS, 0x00},

{AIC3106_REG0_GPIO1_CONTROL, 0x00},

{AIC3106_REG0_GPIO2_CONTROL , 0x00},

{AIC3106_REG0_ADDNL_GPIO_CONTROL_A, 0x00},

{AIC3106_REG0_ADDNL_GPIO_CONTROL_B, 0x01},

{AIC3106_REG0_CLOCK_GEN_CONTROL, 0x02},

{AIC3106_REG0_LEFT_AGC_NEW_ATTACK, 0x00},

{AIC3106_REG0_LEFT_AGC_NEW_DECAY, 0x00},

{AIC3106_REG0_RIGHT_AGC_NEW_ATTACK, 0x00},

{AIC3106_REG0_RIGHT_AGC_NEW_DECAY, 0x00},

{AIC3106_REG0_NEW_ADC_DIGITAL_PATH, 0x00},

{AIC3106_REG0_PASSIVE_ANALOG_BYPASS, 0x00},

{AIC3106_REG0_DAC_QUIESCENT_CURRENT, 0x00}

};