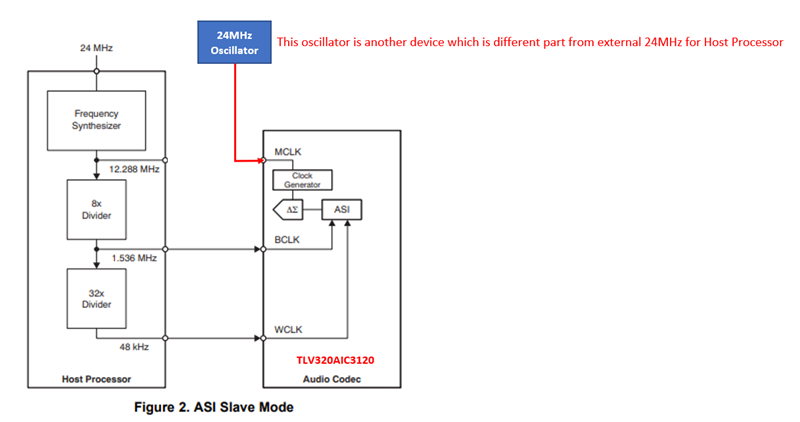

Part Number: TLV320AIC3120

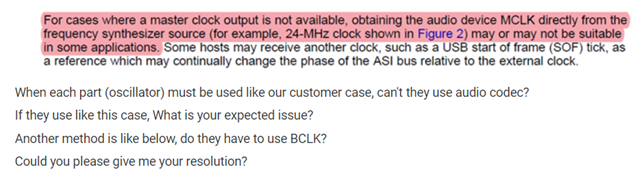

Hello Expert,

Our customer is under design w/ this device.

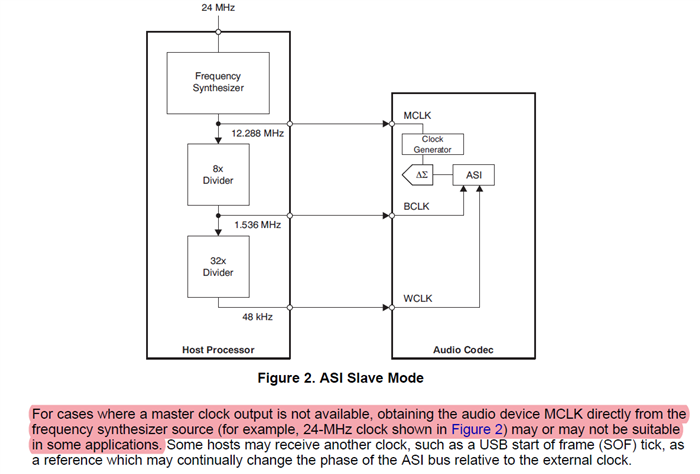

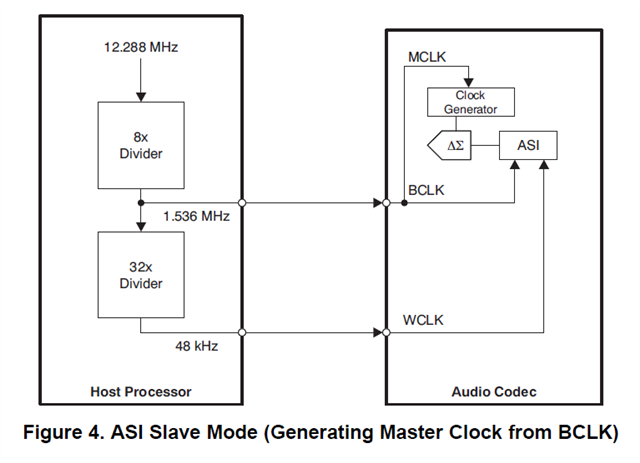

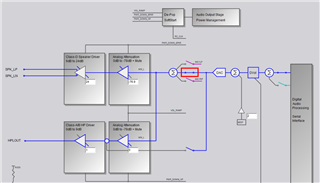

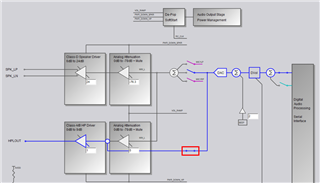

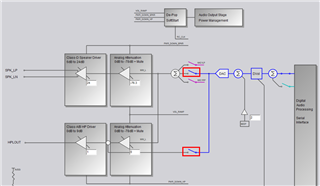

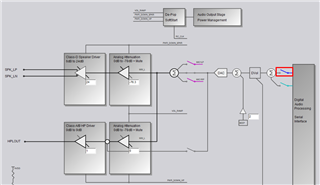

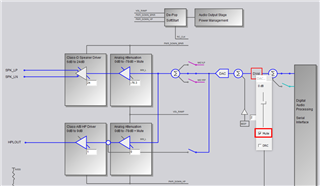

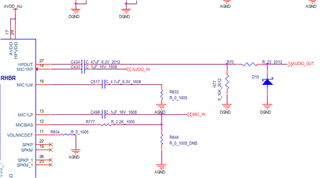

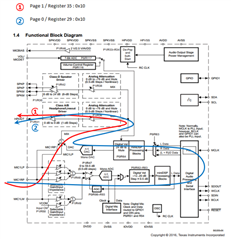

Their board is configured two board which is processor b'd and audio codec b'd.

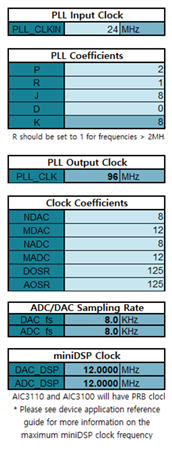

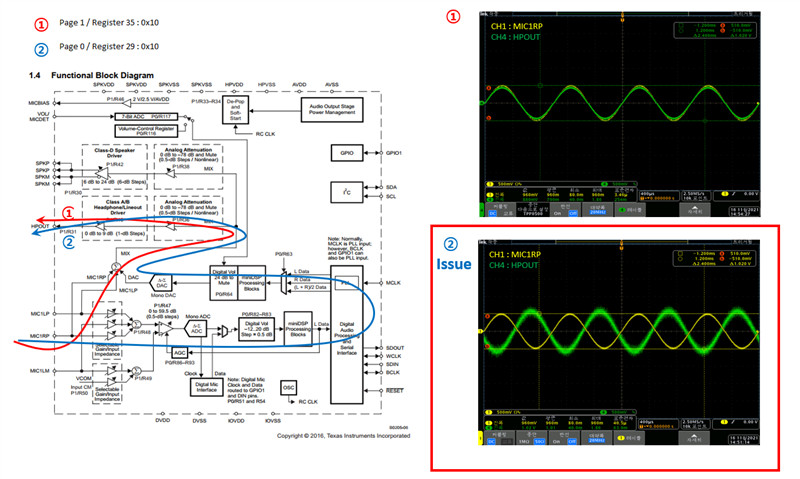

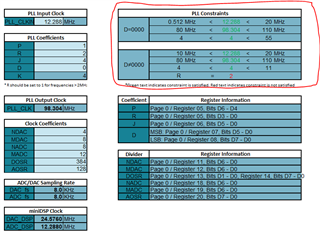

This audio codec can't receive MCLK from processor b'd.

So they have to use another clock source from another oscillator which is different from oscillator of process.

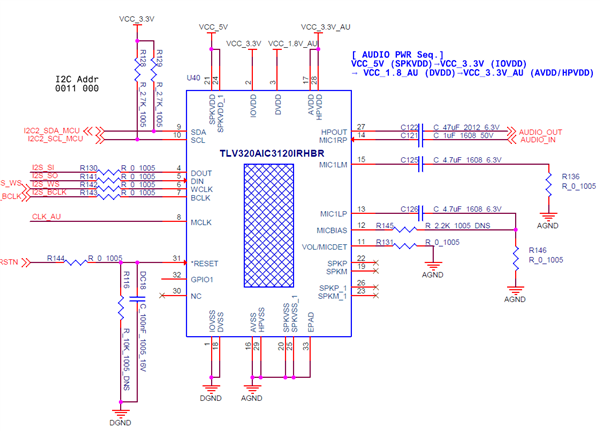

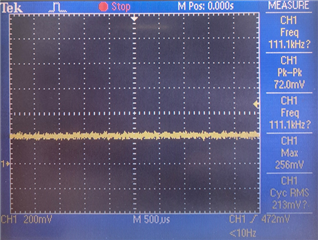

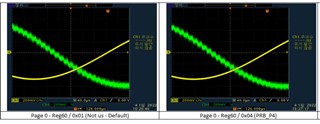

Below is their block diagram to use it.

Is there no problem? Can they use it?

Best Regards,

Michael