I am also having problems with pops on powerup. This is with the initial powering of the circuit, prior to programming the codec.

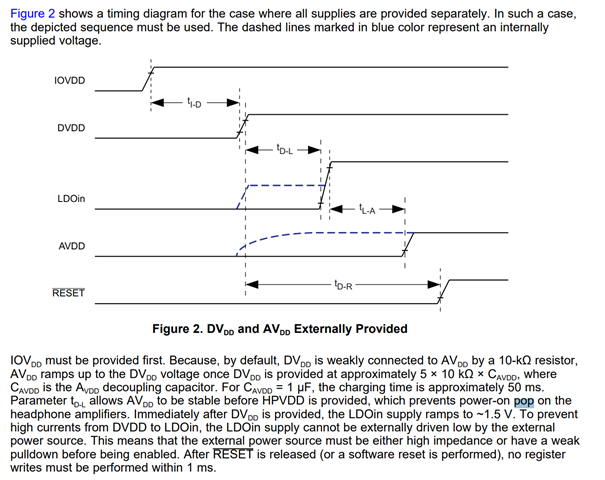

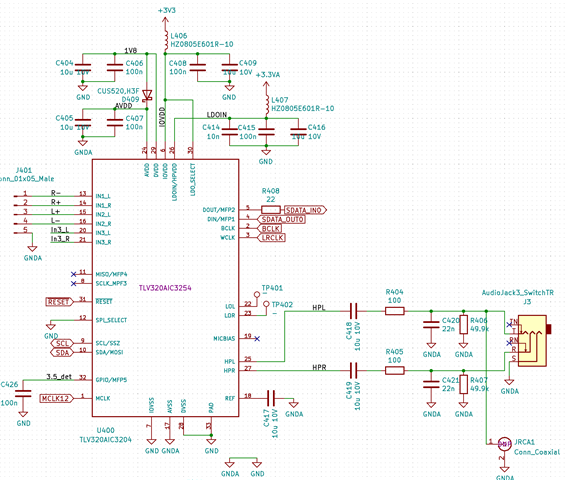

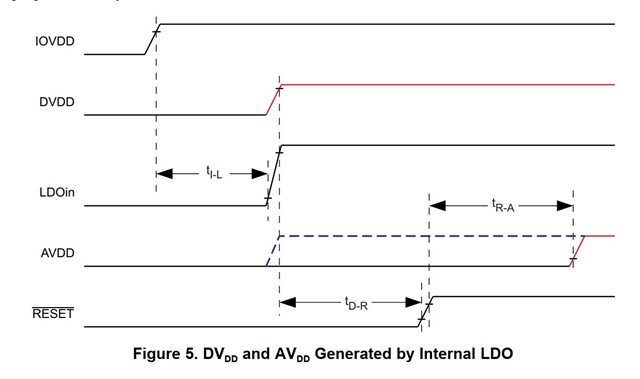

Currently LDOIN and IOVDD are connected together (3.3V), and there is a diode (PMEG3020EJ,115) between AVDD and DVDD as recommended. LDO_SELECT is connected to IOVDD.

If I leave power down long enough to see IOVDD drop below about 0.15V, there is a loud pop when power is applied. Sometimes out of left, sometimes right, sometimes both.

My headphone output circuit is 10u decoupling to 100 ohm in series, then 22n and 47k to GND.

Any ideas on how to mitigate this?

I've tried powering LDOIN separately, and the pop goes with LDOIN being applied.