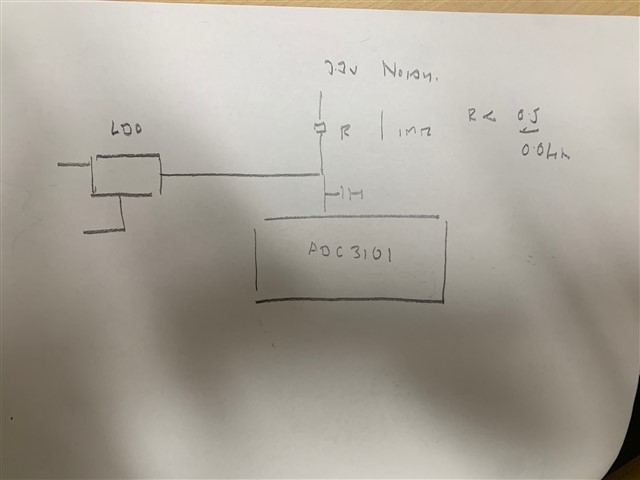

There's a related thread, where I posted about a problem with the LDO (TPS79330) I use to supply the AVDD for the TLV320ADC3101.

One relatively simple solution to that problem would be to disable the AVDD LDO (and the AVDD rail) entirely during the time the application sleeps to conserve battery. Of course, with AVDD = 0V, I don't expect any of the ADC functions to work; the rest of the device will be sleeping as well, so no I²C / I²S traffic would occur.

If the TLV320 can survive AVDD=0 for extended time, my plan of bringing it up upon device wake-up is to:

- Enable the LDO (bringing AVDD to 3.0V) and wait a bit. IOVDD is 3.3V at all times, and DVDD is 1.8V at all times

- Reset the TLV320 and then configure it for recording

When I want to put the device back to sleep, I plan to

- Reset the TLV320 again, to enter the lowest-power state

- Disable AVDD (it would slowly drain to 0V)

- DVDD and IOVDD stay up even during sleep

- This can go on for hours before the next wakeup

I don't see anything mentioned in the datasheet about this scenario. Would the behaviour of the TLV320 be undefined in that case? Could it be damaged by prolonged AVDD=0V while the other rails are powered? Do I need to take any extra steps besides the aforementioned?

Best regards,

Veselin